Сколько разрядов должен иметь двоичный счетчик чтобы обеспечить возможность счета 64 импульсов

Обновлено: 30.06.2024

Понятие "счетчик" является очень широким. К счетчикам относят автоматы, которые под действием входных импульсов переходят из одного состояния в другое, фиксируя тем самым число поступивших на их вход импульсов в том или ином коде.

Классификация счетчиков

По способу кодирования внутренних состояний различают двоичные счетчики, счетчики Джонсона, счетчики с кодом "1 из N" и др.

По направлению счета счетчики делятся на суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные (с изменением направления счета).

По принадлежности к тому или иному классу автоматов говорят о синхронных или асинхронных счетчиках (более подробную классификацию по этому признаку не затрагиваем, учитывая реальный состав микросхем счетчиков).

Счетчики строятся из разрядных схем, имеющих межразрядные связи. Соответственно организации этих связей различают счетчики с последовательным, параллельным и комбинированными переносами.

Возможные режимы работы счетчика:

§ регистрация числа поступивших на счетчик сигналов;

Как и любой автомат, счетчик можно строить на триггерах любого типа, однако удобнее всего использовать для этого триггеры типа Т (счетные) и JK, имеющие при J = К = 1 счетный режим.

Состояние счетчика читается по выходам разрядных схем как слово Qn-1 Qn-2. Q0, входные сигналы поступают на младший разряд счетчика.

Двоичным счетчиком назовем счетчик, имеющий модуль М = 2 n , где n — целое число, и естественную последовательность кодов состояний (его состояния отображаются последовательностью двоичных чисел, десятичными эквивалентами которых будут числа 0, 1, 2, 3. М-1).

Двоичные счетчики

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путем представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до М—1. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101. что естественно, т. к. младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011. . В третьем разряде образуется последовательность из четверок нулей и единиц 00001111. и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный.

Представление счетчика цепочкой Т-триггеров справедливо как для суммирующего, так и для вычитающего вариантов, поскольку закономерность по соотношению частот переключения разрядов сохраняется как при просмотре таблицы сверху вниз (прямой счет), так и снизу вверх (обратный счет). Различия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего. При прямом счете следующий разряд переключается при переходе предыдущего в направлении 1-0, а при обратном— при переключении 0-1. Следовательно, различие между вариантами заключается в разном подключении входов триггеров к выходам предыдущих. Если схема строится на счетных триггерах с прямым динамическим управлением, то характер подключения следующих триггеров к предыдущим для получения счетчиков прямого и обратного счета будет соответствовать рис. 3.43, б.

40. Запоминающие устройства. Основные параметры.

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими ЦУ. Микросхемы памяти в общем объеме выпуска ИС занимают около 40% и играют важнейшую роль во многих системах различного назначения. Микросхемы и системы памяти постоянно совершенствуются как в области схемотехнологии, так и в области развития новых архитектур. В настоящее время созданы и используются десятки различных типов ЗУ.

Важнейшие параметры ЗУ находятся в противоречии. Так, например, большая информационная емкость не сочетается с высоким быстродействием, а быстродействие в свою очередь не сочетается с низкой стоимостью. Поэтому системам памяти свойственна многоступенчатая иерархическая структура, и в зависимости от роли того или иного ЗУ его реализация может быть существенно различной.

В наиболее развитой иерархии памяти ЭВМ можно выделить следующие уровни:

- регистровые ЗУ, находящиеся в составе процессора или других устройств (т. е. внутренние для этих блоков), благодаря которым уменьшается число обращений к другим уровням памяти, реализованным вне процессора и требующим большего времени для операций обмена информацией;

- кэш-память, служащая для хранения копий информации, используемой в текущих операциях обмена. Высокое быстродействие кэш-памяти повышает производительность ЭВМ;

- основная память (оперативная, постоянная, полупостоянная), работающая в режиме непосредственного обмена с процессором и по возможности согласованная с ним по быстродействию. Исполняемый в текущий момент фрагмент программы обязательно находится в основной памяти;

- специализированные виды памяти, характерные для некоторых специфических архитектур (многопортовые, ассоциативные, видеопамять и др.);

- внешняя память, хранящая большие объемы информации. Эта память обычно реализуется на основе устройств с подвижным носителем информации (магнитные и оптические диски, магнитные ленты и др.). В настоящем пособии устройства внешней памяти не рассматриваются.

Важнейшие параметры ЗУ

Информационная емкость — максимально возможный объем хранимой информации. Выражается в битах или словах (в частности, в байтах). Бит хранится запоминающим элементом (ЗЭ), а слово — запоминающей ячейкой (ЗЯ), т. е. группой ЗЭ, к которым возможно лишь одновременное обращение. Добавление к единице измерения множителя "К" (кило) означает умножение на 2 10 = 1024, а множителя "М" (мега) — умножение на 2 20 = 1048576.

Организация ЗУ— произведение числа хранимых слов на их разрядность. Видно, что это дает информационную емкость ЗУ, однако при одной и той же информационной емкости организация ЗУ может быть различной, так что организация является самостоятельным важным параметром.

Быстродействие (производительность) ЗУ оценивают временами считывания, записи и длительностями циклов чтения/записи. Время считывания — интервал между моментами появления сигнала чтения и слова на выходе ЗУ.

Время чтения, записи и длительности циклов — традиционные параметры. Для некоторых современных ЗУ они должны быть дополнены новыми. Причиной является более сложный характер доступа к хранимым данным, когда обращение к первому слову некоторой группы слов (пакета) требует большего времени, чем обращение к последующим. Помимо указанных основных параметров для ЗУ указывают еще целый набор временных интервалов. Перечисленные выше динамические параметры являются эксплуатационными (измеряемыми). Кроме них, существует ряд режимных параметров, обеспечение которых необходимо для нормального функционирования ЗУ, поскольку оно имеет несколько сигналов управления, для которых должно быть обеспечено определенное взаимное расположение во времени. Для этих сигналов задаются длительности и ограничения по взаимному положению во времени.

Время записи — интервал после появления сигнала записи, достаточный для установления ЗЯ в состояние, задаваемое входным словом. Минимально допустимый интервал между последовательными чтениями или записями образует соответствующий цикл. Длительности циклов могут превышать времена чтения или записи, т. к. после этих операций может потребоваться время для восстановления необходимого начального состояния ЗУ.

Рис. 4.1. Типичные сигналы ЗУ (а) и их временные диаграммы (б)

Классификация ЗУ.

Для классификации ЗУ (рис. 4.2) важнейшим признаком является способ доступа к данным.

При адресном доступе код на адресном входе указывает ячейку, с которой ведется обмен. Все ячейки адресной памяти в момент обращения равнодоступны. Эти ЗУ наиболее разработаны, и другие виды памяти часто строят на основе адресной с соответствующими модификациями.

Адресные ЗУ делятся на RAM (Random Access Memory) u ROM (Read-Only Memory). Русские синонимы термина RAM: ОЗУ (оперативные ЗУ) или ЗУПВ (ЗУ с произвольной выборкой). Оперативные ЗУ хранят данные, участвующие в обмене при исполнении текущей программы, которые могут быть изменены в произвольный момент времени. Запоминающие элементы ОЗУ, как правило, не обладают энергонезависимостью.

В ROM (русский эквивалент — ПЗУ, т. е. постоянные ЗУ) содержимое либо вообще не изменяется, либо изменяется, но редко и в специальном режиме. Для рабочего режима это "память только для чтения".

Рис. 4.2. Классификация полупроводниковых ЗУ

RAМ делятся на статические и динамические. В первом варианте запоминающими элементами являются триггеры, сохраняющие свое состояние, пока схема находится под питанием и нет н овой записи данных. Регенерация данных в динамических ЗУ осуществляется с помощью специальных контроллеров. Разработаны также ЗУ с динамическими запоминающими элементами, имеющие внутреннюю встроенную систему регенерации, у которых внешнее поведение относительно управляющих сигналов становится аналогичным поведению статических ЗУ. Такие ЗУ называют квазистатическими.

Статические ЗУ называются SRAM (Static RAM), а динамические — DRAM (Dynamic RAM).

Статические ОЗУ можно разделить на асинхронные, тактируемые и синхронные (конвейерные). В асинхронных сигналы управления могут задаваться как импульсами, так и уровнями. В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными, например, сигнал разрешения работы CS в каждом цикле обращения к памяти должен переходить из пассивного состояния в активное (должен формироваться фронт этого сигнала в каждом цикле). Этот тип ЗУ называют часто синхронным. Здесь использован термин "тактируемые", чтобы "освободить" термин "синхронные" для новых типов ЗУ, в которых организован конвейерный тракт передачи данных, синхронизируемый от тактовой системы процессора, что дает повышение темпа передач данных в несколько раз.

Динамические ЗУ характеризуются наибольшей информационной емкостью и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ. Поскольку от этой памяти требуется высокое быстродействие, разработаны многочисленные архитектуры повышенного быстродействия, перечисленные в классификации.

Постоянная память типа ROM (M) программируется при изготовлении методами интегральной технологии с помощью одной из используемых при этом масок. В русском языке ее можно назвать памятью типа ПЗУМ (ПЗУ масочные). Для потребителя это в полном смысле слова постоянная память, т. к. изменить ее содержимое он не может.

Это программируемая пользователем память (в русской терминологии ППЗУ — программируемые ПЗУ). Ее содержимое записывается либо однократно (в PROM),либо может быть заменено путем стирания старой информации и записи новой (в EPROM и EEPROM). В EPROM стирание выполняется с помощью облучения кристалла ультрафиолетовыми лучами, ее русское название РПЗУ-УФ (репрограммируемое ПЗУ с УФ-стиранием). В EEPROM стирание производится электрическими сигналами, ее русское название РПЗУ-ЭС (репрограммируемое ПЗУ с электрическим стиранием). Английские названия расшифровываются как Electrically Programmable ROM и Electrically Erasable Programmable ROM. Программирование PROM и репрограммирование EPROM и EEPROM производятся в обычных лабораторных условиях с помощью либо специальных программаторов, либо специальных режимов без специальных приборов (для EEPROM).

Память типа Flash по запоминающему элементу подобна памяти типа EEPROM (или иначе E 2 PROM), но имеет структурные и технологические особенности, позволяющие выделить ее в отдельный вид.

Запись данных и для EPROM и для E 2 PROM производится электрическими сигналами.

В ЗУ с последовательным доступом записываемые данные образуют некоторую очередь. Считывание происходит из очереди слово за словом либо в порядке записи, либо в обратном порядке.

Прямой порядок считывания имеет место в буферах FIFO с дисциплиной "первый пришел — первый вышел" (First In — First Out), а также в файловых и циклических ЗУ.

Разница между памятью FIFO и файловым ЗУ состоит в том, что в FIFO запись в пустой буфер сразу же становится доступной для чтения, т. е. поступает в конец цепочки (модели ЗУ). Прием данных из файлового ЗУ начинается после обнаружения приемником символа начала блока.

В циклических ЗУ слова доступны одно за другим с постоянным периодом, определяемым емкостью памяти. К такому типу среди полупроводниковых ЗУ относится видеопамять (VRAM).

Считывание в обратном порядке свойственно стековым ЗУ, для которых реализуется дисциплина "последний пришел — первый вышел". Такие ЗУ называют буферами LIFO (Last In — First Out).

Счетчиками называют последовательные цифровые устройства, предназначенные для подсчета и запоминания числа импульсов, поданных в определенном временном интервале на его счетный вход. Помимо счетного счетчики могут еще иметь входы асинхронный или синхронной установки начальных состояний. По характеру изменения состояний счетчика счетными импульсами различают суммирующие, вычитающие и реверсивные счетчики. По способу организации переносов между разрядами их можно разделить на счетчики с последовательным, сквозным, параллельным и комбинированным переносом. Счетчики с последовательным и сквозным переносом называют асинхронными, а с параллельным переносом – синхронными. Обычно счетчик содержит одни или несколько идентичных разрядов, построенных на основе двоичных триггеров. Количество различимых состояний разряда счетчика является его классификационным признаком, согласно которому счетчики называют двоичными, двоично-десятичными и т. д.

Счетчики и делители подразделяются на асинхронные и синхронные. У синхронных счетчиков все разрядные триггеры синхронизируются параллельно одними и теми же синхроимпульсами, поступающими из источника этих импульсов. Асинхронные счетчики имеют последовательную синхронизацию, т.е. каждый последующий разрядный триггер синхронизируется выходными импульсами триггера предыдущего разряда. Асинхронные счетчики иногда называют последовательными, а синхронные счетчики - параллельными.

Синхронные счетчики, в свою очередь, подразделяются на параллельно-синхронные и последовательно-синхронные. Параллельные счетчики имеют более высокую скорость счета, чем асинхронные.

Счетчики, независимо от способа синхронизации, подразделяются на счетчики прямого счета (суммирующие) и на счетчики обратного счета (вычитающие). В интегральном исполнении выпускаются также реверсивные счетчики, в которых имеется специальный вход для переключения режима работы, т.е. направления счета. Многие типы счетчиков, выпускаемые промышленностью в интегральном исполнении, имеют дополнительные входы предустановки, позволяющие использовать эти счетчики в режиме регистра памяти.

В качестве разрядных триггеров счетчиков и делителей могут быть использованы двухступенчатые D-триггеры, Т- и JK-триггеры.

Асинхронный двоичный счетчик. Асинхронный двоичный счетчик представляет собой совокупность последовательно соединенных триггеров (D - или JK), каждый из которых ассоциируется с битом в двоичном представлении числа. Если в счетчике m триггеров, то число возможных состояний счетчика равно 2 m , и, следовательно, модуль счета М также равен 2 m . Счетная последовательность в двоичном суммирующем счетчике начинается с нуля и доходит до максимального числа 2 m - 1, после чего снова проходит через нуль и повторяется. В вычитающем двоичном счетчике последовательные двоичные числа перебираются в обратном порядке, и при повторении последовательности максимальное число следует за нулем.

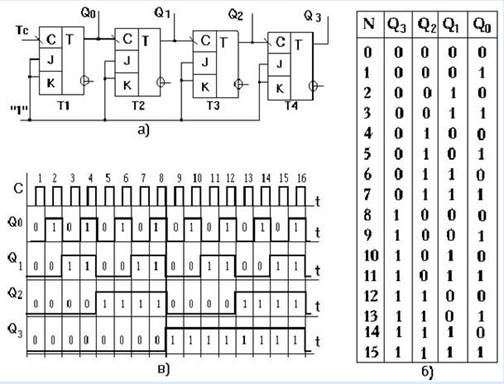

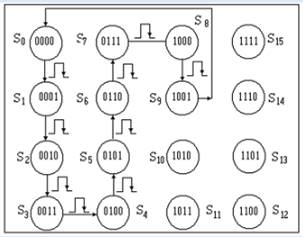

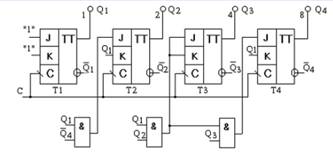

Рассмотрим устройство двоичного суммирующего счетчика по модулю М=16, выполненного на базе JK-триггеров (рисунок. 1, а).

Как видно из рисунке. 1 (а), синхронизирующие входы всех триггеров, кроме крайнего левого (Т1), соединены с выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния предыдущего триггера.

Рисунок. 1 - Схема а), таблица состояний триггеров б) и временные диаграммы, поясняющие работу в) последовательного четырехразрядного счетчика на JK - триггерах

Временные диаграммы, поясняющие работу асинхронного суммирующего счетчика приведены на рис. 1, в.

Рисунок 2 - Схема временные диаграммы вычитающего трехразрядного счетчика на D - триггерах

В некоторых случаях необходимо, чтобы счетчик мог работать как в прямом, так и в обратном направлении счета. Такие счетчики называются реверсивными. Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Так, например, асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода предыдущего JK- или Т-триггера на счетный вход последующего. В случае, когда реверсивный счетчик строится на базе D-триггеров, управляемых передним фронтом, для получения режима прямого счета следует соединить инверсный выход предыдущего со счетным входом последующего триггера.

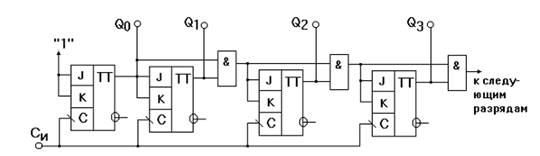

Параллельные счетчики (синхронные счетчики). Как было уже сказано выше, параллельные счетчики бывают двух типов: синхронные параллельные и синхронные последовательные.

Рисунок 3 - Синхронный последовательный суммирующий счетчик на JK – триггерах

Синхронный последовательный счетчик. По способу подачи синхроимпульсов такие счетчики параллельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно, а по способу управления (подачи управляющих импульсов) - последовательные. Схема синхронного последовательного счетчика, реализованного на JK-триггерах, приведена на рис. 3.

Рисунок 4 - Параллельный синхронный счетчик на JK - триггерах

Поскольку счетчик имеет одну общую линию синхронизации, состояние триггеров меняется синхронно, т.е. те триггеры, которые по синхроимпульсу должны изменить свое состояние, делают это одновременно, что существенно повышает быстродействие синхронных счетчиков.

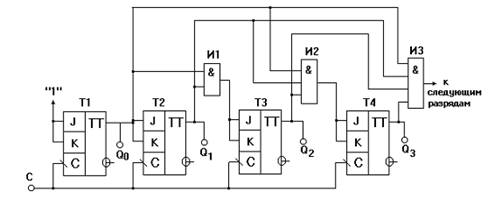

Счетчики с произвольным коэффициентом счета. Принцип построения подобного класса счетных устройств состоит в исключении нескольких состояний обычного двоичного счетчика, являющихся избыточными для счетчиков с коэффициентом пересчета, отличающимися от двоичных. При этом избыточные состояния исключаются с помощью обратных связей внутри счетчика.

Число избыточных состояний для любого счетчика определяется из следующего выражения:

где М - число запрещенных состояний, Ксч - требуемый коэффициент счета; 2 m - число устойчивых состояний двоичного счетчика.

Задача синтеза счетчика с произвольным коэффициентом счета заключается в определении необходимых обратных связей и минимизации их числа. Требуемое количество триггеров определяется из выражения

где [log2 Ксч] - двоичный логарифм заданного коэффициента пересчета Ксч, округленный до ближайшего целого числа.

Рисунок 5 - Пример реализации счетчика с Kсч=10

Как следует из рис. 5, роль ячейки, выявляющей факт достижения кодовой комбинации 1010 на выходах счетчика, играет ячейка И, уже имеющаяся на входе сброса ИМС К1533ИЕ5.

Рассмотрим пример синтеза синхронного двоично-десятичного счетчика на базе JK-триггеров. На рисунке 6 показан граф, поясняющий последовательность переходов десятичного счетчика, в таблице 2 - таблица переходов.

Рисунок 6 - Граф переходов двоично-десятичного счетчика

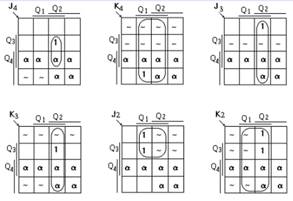

Рисунок 7 - Карты Карно для функции комбинационной логики двоично-десятичного счетчика

На рис. 7 приведены карты Карно для логических функций, которым должны соответствовать сигналы, присутствующие на управляющих входах триггеров (нулевые значения функций в клетки карты Карно не записаны).

; ; (3)

; ;

; .

На рис. 8 показана схема двоично-десятичного синхронного счетчика.

Если счетчик из-за какой-либо неисправности окажется в одном из запрещенных (неиспользуемых) состояний, то его работа может быть прервана специальным сигналом и также может быть подан сигнал тревоги о неисправности в схеме счетчика. Обнаружить это позволяет схема, реализующая выражение, описывающее функцию неиспользуемых состояний

Рисунок 8 - Схема реализации двоично-десятичного синхронного счетчика

Задания к практической работе

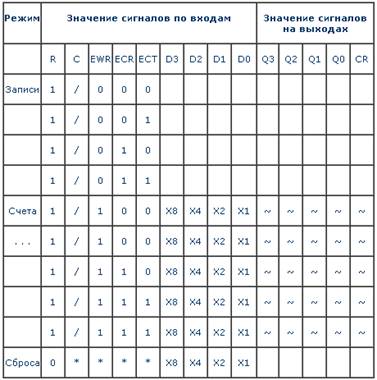

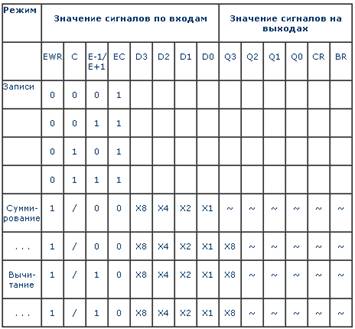

Задание 1. Начертить УГО счетчиков и построить временные диаграммы их работы в режимах счета и записи информации. Построить таблицу режимов работы счетчиков по форме таблицы 3 и таблицы 4.

Задание 2 . Исследовать работу счетчиков при одиночных импульсах по входу счета в различных режимах: сначала без, а затем с предварительной записью информации. Сделать выводы по результатам экспериментов.

Задание 3 . Собрать схему последовательного 4-х разрядного двоичного счетчика:

Выходы соединить с любыми гнездами индикатора на вспомогательном устройстве; свечение светодиода свидетельствует о наличии на выходе сигнал лог.1.

Произвести сброс счетчика в нулевое состояние, для чего на вход R (уст.0) подать отрицательный импульс;

Таблица 3 - Режимы работы ИМС К155ИЕ9

Таблица 4 - Режимы работы ИМС К155ИЕ13

Задание 4 . Решите задачу. Каждое показание счётчика, фиксируемое в памяти компьютера, занимает 10 бит. Записано 100 показаний этого датчика. Каков информационный объём снятых значений в байтах?

Задание 5 . Постройте счётчик для указанных модулей счёта:

Контрольные вопросы и задания

1. Чему равны Kсч. Восьмиразрядного двоичного и восьмиразрядного двоично-десятичного счетчиков?

2. Изобразите структурную схему и временные диаграммы работы трехразрядного двоичного вычитающего счетчика на основе T-триггеров с инверсным динамическим счетным входом.

3. В чем отличие схем и принципов функционирования счетчиков с параллельным и сквозным переносами?

4. В чем заключается принцип построения недвоичных счетчиков и как реализовать счетчик с Ксч .=8 на базе двоичных счетчиков?

5. Назовите основные типы и параметры счетчиков.

6. Составьте схему и постройте временные диаграммы работы последовательного трехразрядного двоичного счетчика. Объяснить его работу.

7. Составьте схему и постройте временные диаграммы работы параллельного трехразрядного двоичного счетчика.

8. Составьте схему и постройте временные диаграммы работы счетчика Джонсона. Объяснить его работу.

9. Составьте схему двоично-десятичного по заданной преподавателем таблице переходов.

10. Составьте схему недвоичного счетчика с модулем пересчета М=5,6,7,11. Объяснить его работу.

11. Составьте схему счетчика делителя с коэффициентом пересчета М=4,6,9,11.

В современных электронных вычислительных машинах применяется двоичная система счисления, удобная для программирования, т.к. машина легко различает два противоположных состояния - 0 и 1.

Практически любую аналоговую величину (длительность и период повторения импульсов, угол поворота, перемещение, скорость и т. п.) можно преобразовать в электрические импульсы, число которых пропорционально значению аналоговой величины. Подсчитать эти импульсы можно с помощью счетчика и выразить числом или кодом. В ЭВМ счетчики применяются для формирования адресов команд, подсчета количества циклов при выполнении программы, подсчета количества шагов при выполнении операций умножении и деления. Счетчики обозначают через СТ (от англ. counter).

Счетчики импульсов выполняются на основе триггеров, образующих двоичные разряды. Количество разрядов определяется наибольшим числом, которое должен зафиксировать счетчик.

Рассмотрим различные типы триггерных СТ, как они устроены и работают.

Двоичные счетчики.

Они используют двоичную систему счисления, как в таблице 1.

На рис.1а показан простейший асинхронный счетчик , построенный из четырех Т-триггеров.

Т-триггеры подключены последовательно, каждое из которых делит на 2. По входному сигналу первый триггер делит на 2, второй - на 2² = 4, третий - 2³ = 8 и четвертый - на 2 4 = 16. Таким образом, это разное количество полученных импульсов, считываются с выходов Q1 - Q4.

Информация представлена в двоичном (бинарном) коде и воспринимается справа налево, т.е. на четырех выходах появляются единицы, двойки, четверки и восьмерки.

Рассматриваемый СТ имеет объем 16. Срабатывание заданного триггера осуществляется за счет смены предыдущего триггера, т.е. здесь нет синхронизирующего сигнала.

На рис.1б показан синхронный счетчик , умеющий дополнительный тактовый вход C. При помощи этого управляющего сигнала выполняется активация четырех триггеров для подготовки их к изменению своего состояния.

На рис.1c показаны временные диаграммы двоичных счетчиков, если нет задержки сигналов. В этом случае активным является отрицательный фронт, отмеченный стрелкой.

Первый триггер возвращается к исходному состоянию после двух входных импульсов, второй - после четырех импульсов, третий - после восьми и четвертый - после шестнадцати входных импульсов.

Обратите внимание, что здесь счет начинается с 0 и заканчивается на 15. Когда на вход подается шестнадцатый импульс, весь СТ начинает работать с самого начала. т.е. состояние всех выходов равно нулю.

Кроме тактового входа, показанного на рис.1б, реальные счетчики имеют еще один управляющий вход, который фиксирует начало счета, когда, например, когда все Т-триггеры сброшены.

На основе представленной схемы можно построить СТ для любого числа, добавляя дополнительные триггеры. Если требуется считать до десятичного числа A , то общее количество n триггеров определяется так: 2 n > A . Например, если нужно считать до 100, тогда триггеров нужно семь: 2 7 = 128.

Рассматриваемый до сих пор счетчик, еще называют суммирующим . В нем каждый следующий импульс увеличивает на единицу значение, записанное в триггере. Это так называемый нормальный счет.

Кроме того, существуют вычитающие счетчики . Для них характерно то, что каждый последующий входной импульс уменьшает на единицу запись триггера. В них в начальном состояние на всех выходах - логическая 1.

Например, если триггеров четыре, то при отсутствии входного сигнала на выходах будет двоичное число 1111. При получении первого импульса число на выходах будет 1110, второго - 1101, третьего - 1100 и т.д. Это видно из таб.1, если смотреть снизу вверх.

Есть еще, так называемые, реверсивные счетчики . Они могут работать как суммирующие или вычитающие. Помимо входа для подсчета есть и дополнительный вход, через который определяется, является ли СТ суммирующий или вычитающий.

На практике это можно реализовать с помощью T-, D- и JK-триггеров и др.

Десятичные счетчики.

Делители частоты.

Это устройства, на вход которых поступают импульсы с частотой fвх , а на выходные импульсы с частотой fвых . Отношение N = fвx / fвых называется коэффициентом деления и является их важнейшим параметром.

Мы уже видели, что при помощи двоичных и десятичных счетчиков легко получить делители на 2 и 10 (соответственно 2 n и 10 n ). Однако есть устройства, такие как часовой механизм, где необходимо делители на 12, 24 и 60, а также сетевой преобразователь частота 50 Гц в 60 импульсов.

Существуют разные типы схем с коэффициентом деления от 1 до 99. В дополнение к упомянутым делителям 2 и 10 на практике используются делители 3, 5, 6 и 7. Они могут быть реализовано как с TTL ИС, так и с SMOS ИС. Есть еще удвоители частоты, но используются они редко.

На рис.3 показаны две схемы - с коэффициентом деления N = 3 u N = 5, которые реализованы с помощью JK-триггеров.

При соединении несколько делителей последовательно, результирующий коэффициент равен произведению их коэффициентов. Например, если N1 = 3 и N2 = 5, результирующий коэффициент делителя будет Nрез = 3·5 = 15.

Также существуют так называемые программируемые делители частоты . Им коэффициент деления устанавливается извне двоично-десятичным кодом, для этого делитель имеет 4 дополнительных входа.

Например таким программируемым синхронным счетчиком в интегральном варианте является схема 74161, где коэффициент деления можно установить в диапазоне от 1 до 16.

В устройствах цифровой обработки информации измеряемый параметр (угол поворота, скорость, давление и т. п.) преобразуются в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счётчиками импульсов и выражаются в виде цифр.

Основными показателями счётчиков являются ёмкость и быстродействие.

Ёмкость , численно равная КСЧ , характеризует число импульсов, доступное счёту за один цикл. Как уже было показано выше, ёмкость определяется количеством разрядов счётчика.

Быстродействие или максимально возможная скорость работы оценивается двумя параметрами:

– Разрешающая способность tраз.сч — минимальное время между двумя входными сигналами, в течение которого ещё не возникают сбои в работе счётчика. Величина, обратная разрешающей способности, называется максимальной частотой счёта f max. f max определяет количество импульсов, которое может подсчитать счётчик за 1 сек.

– Время установки кода счётчика tуст — это время между моментом прихода входного сигнала и переходом счётчика в новое устойчивое состояние.

Для удовлетворения потребностей разработчиков цифровых электронных устройств различного назначения разработаны интегральные микросхемы счётчиков с широким спектром параметров. Всё многообразие счётчиков можно классифицировать по следующим признакам.

1 По направлению счёта:

2 По коэффициенту счёта:

• С постоянным произвольным коэффициентом счёта,

• С переменным коэффициентом счёта.

3 По способу организации внутренних связей:

• С последовательным переносом,

• С параллельным переносом,

• С комбинированным переносом,

Классификационные признаки независимы и могут встречаться в разных сочетаниях. Например, суммирующие счётчики могут быть как с последовательным, так и с параллельным переносом и могут иметь двоичный или десятичный коэффициент счёта.

5.3.2 Суммирующие счётчики

Простейшим счётчиком является Т-триггер, считающий до 2-х, то есть осуществляющий счёт и хранение не более 2-х сигналов.

Счётчик, образованный цепочкой из n триггеров сможет подсчитать в двоичном коде 2 n импульсов. Число n определяет количество разрядов двоичного числа, которое может быть записано в счётчик. Число 2 n называется модулем или коэффициентом счёта :

Схема простейшего 4-х разрядного счётчика приведена на рисунке 60,а. Принцип работы счётчика проиллюстрирован временными диаграммами, приведёнными на рисунке 60,б.

Рисунок 60 Схема двоичного суммирующего счётчика а)

и временные диаграммы его работы б).

Первый разряд счётчика переключается с приходом каждого входного импульса, что соответствует алгоритму работы Т-триггера. На каждые два входных импульса Т-триггер формирует один выходной импульс.

Третий разряд — после прихода каждого 4-го импульса.

Таким образом, единичные значения сигналов на выходах триггеров регистра появляются с приходом 1, 2, 4, 8 импульсов, что соответствует весовым коэффициентам двоичного кода. Поэтому с выходов триггеров регистра можно прочитать параллельный двоичный код числа импульсов, поступивших на его вход. Например, после прихода 5 импульсов единичные значения установятся на выходах Q1 и Q3 (см. пунктирную линию на рисунке 60,б), что соответствует коду числа 5: 0101B. Аналогично, после прихода 13-и импульсов на выходах триггеров установится код 1101B.

Если число входных импульсов NВХ > KСЧ , то при NВХ=KСЧ происходит переполнение счётчика, после чего счётчик возвращается в нулевое состояние и повторяет цикл работы.

После каждого цикла счёта на выходе последнего триггера возникают перепады напряжения, то есть формируется один импульс. Это свойство определяет второе назначение счётчиков — деление числа входных импульсов.

Если входные сигналы периодичны и следуют с частотой fВХ , то частота fВЫХ :

В этом случае коэффициент счёта определяется как коэффициент деления и обозначается KДЕЛ .

У счётчика в режиме деления частоты используется сигнал только последнего триггера, а промежуточные состояния остальных триггеров не учитываются.

Всякий счётчик может быть использован как делитель частоты.

5.3.3 Вычитающие и реверсивные счётчики

Реверсивный счётчик может работать в качестве суммирующего и вычитающего.

Суммирующий счётчик , как было показано выше, получается при подсоединении к входу последующего каскада прямого выхода предыдущего.

Каждый входной импульс увеличивает число, записанное в счётчик, на 1. Перенос информации из предыдущего разряда в последующий происходит при смене состояния предыдущего разряда (триггера) с 1 на 0.

Вычитающий счётчик получается при подсоединении к входу последующего каскада инверсного выхода предыдущего. Он действует обратным образом: двоичное число, хранящееся в счётчике, с каждым поступающим импульсом уменьшается на 1.

Перенос из младшего разряда в старший имеет место при смене состояния младшего разряда с 0 на 1.

Переполнение происходит после достижения счётчиком нулевого состояния, при этом в счётчик записывается максимально возможное значение, т.е. во все разряды — единицы.

Путём включения в схему двоичного суммирующего счётчика (рисунок 60), дополнительных ЛЭ, переключающих на вход последующего триггера прямого и инверсного выходов предыдущего, получается схема реверсивного счётчика. Фрагмент схемы реверсивного счётчика приведён на рисунке 61.

Рисунок 61 Фрагмент схемы реверсивного счётчика

Схема имеет два входа для подачи входных сигналов: +1 — при работе в режиме суммирования, -1 — при работе в режиме вычитания. Дополнительный управляющий вход N задаёт направление счёта. При N=0 схема (рисунок 61) работает как суммирующий счётчик, а при N=1 — как вычитающий.

5.3.4 Счётчики с произвольным коэффициентом счёта

В двоичных счётчиках коэффициент счёта KСЧ =2 n и может быть равен 2, 4, 8, 16, 32 и т.д. На практике требуются счётчики с коэффициентом счёта не равным 2 n , например, 3, 6, 10, 12, 24 и др.

Например, двоично-десятичный (декадный) счётчик получают из 4-х разрядного, имеющего KСЧ =16, исключая 6 состояний.

Возможны 2 варианта построения схем:

а) Счёт циклически идёт от 0000 до 1001, а следующим импульсом обнуляется;

б) Исходным состоянием служит код 0110 числа 6 и счёт происходит до 11112=15, а следующим импульсом обнуляется.

Рисунок 62 Схема счётчика с Ксч =10

Для реализации схемы по второму варианту используются триггеры, имеющие входы асинхронной установки триггера .

5.3.5 Счётчики с последовательно-параллельным переносом

Все рассмотренные выше схемы счётчиков представляют собой счётчики с последовательным переносом . В этих счётчиках импульсы, подлежащие счёту, поступают на вход только одного первого триггера, а сигнал переноса передаётся последовательно от одного разряда к другому. Такие счётчики отличаются простотой схемы, но имеют невысокое быстродействие.

Счётчики с параллельным переносом строятся на синхронных триггерах.

Счётные импульсы подаются одновременно на тактовые входы всех триггеров, а каждый из триггеров цепочки служит по отношению к последующим только источником сигналов. Срабатывание триггеров параллельного счётчика происходит синхронно, и задержка переключения всего счётчика равна задержке для одного триггера. Следовательно, такие счётчики более быстродействующие. Их основным недостатком является большая мощность, потребляемая от источника входных сигналов, так как входные импульсы подаются на тактовые входы всех триггеров.

Для устранения недостатков рассмотренных выше счётчиков разработаны и используются счётчики с последовательно-параллельным переносом.

В счётчиках с последовательно-параллельным переносом триггеры объединены в группы так, что отдельные группы образуют счётчики с параллельным переносом, а группы соединяются с последовательным переносом. В роли групп могут быть и готовые счётчики.

Общий коэффициент счёта таких счётчиков равен произведению коэффициентов счёта всех групп.

В качестве примера рассмотрим счётную декаду на JK-триггерах, приведённую на рисунке 63.

Рисунок 63 Счётная декада на JK-триггерах

Схема состоит из двух групп. Первая группа — это триггер DD1.

Вторая группа, состоящая из трёх триггеров DD2–DD4, представляет собой счётчик с параллельным переносом и тактируется выходным сигналом первого триггера. Группы соединены между собой последовательно.

Схема работает следующим образом.

10-ый импульс восстанавливает нулевое состояние 4-го триггера и цикл работы счётчика повторяется.

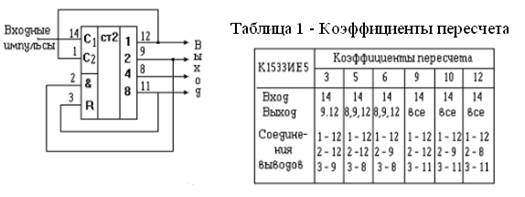

5.3.6 Универсальные счётчики в интегральном исполнении (Примеры)

УГО которых приведены на рисунке 64 а, б, в представляют собой счётчики с последовательно-параллельным переносом, структурные схемы которых подобны схеме, приведённой на рисунке 63.

Рисунок 64 Микросхемы счётчиков К155ИЕ2, К155ИЕ4 и К155ИЕ5

Структурные схемы счётчиков содержат по 4-е JK-триггера в счётном режиме. Первый триггер имеет отдельный вход C1 и прямой выход — 1, три оставшиеся триггера соединены между собой так, что образуют параллельные счётчики с коэффициентами счёта равными 5 (К15ИЕ2), 6 (К155ИЕ4) и 8 (К1ИЕ5).

При соединении выхода первого триггера со входом C2 цепочки из 3-х триггеров образуются счётчики с коэффициентами счёта 10, 12 и 16 соответственно.

На рисунке 61,г показано преобразование счётчика, имеющего KСЧ =12, в десятичный.

Реверсивные счётчики К155ИЕ6 и К155ИЕ7 (Рисунок 65)

Рисунок 65 Реверсивные счётчики К155ИЕ6 а) и К15ИЕ7 б).

Уровни на выходах 1–2–4–8 соответствуют состоянию счёта в данный момент времени.

Отрицательный импульс на выходе ≥9 (≥15) формируется одновременно с 10 (или 16) импульсом на входе +1. Этот импульс может подаваться на вход +1 следующей МС многоразрядного счётчика. При обратном счёте входные импульсы подаются на вход –1, выходные импульсы снимаются с выхода ≤0.

Счётчик-делитель частоты с переменным коэффициентом деления К155ИЕ8 (Рисунок 66).

Микросхема содержит 6-разрядный двоичный счётчик, элементы совпадения и элемент собирания. Элементы совпадения блокируют прохождение импульсов, не совпадающих с запрограммированным кодом, а элемент собирания позволяет передавать на выход только выделенные импульсы.

Рисунок 66 Счётчик – делитель частоты К155ИЕ8

В результате средняя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов.

Читайте также:

- Голикова татьяна гражданство какой страны имеет

- Россию как правовое государство характеризует принцип отделения религии от государства

- Сколько по времени занимает трудоустройство в мвд

- Кто имеет право на ведение власти от имени народа в рк

- Как поступить в случае вымогательства или провокации взятки подкупа