Какие команды осуществляет процессор

Обновлено: 25.06.2024

По функциональному признаку все команды процессора можно разделить на следующие группы:

1) команды пересылки данных и ввода – вывода;

2) команды арифметических и поразрядных логических операций;

3) команды передачи управления.

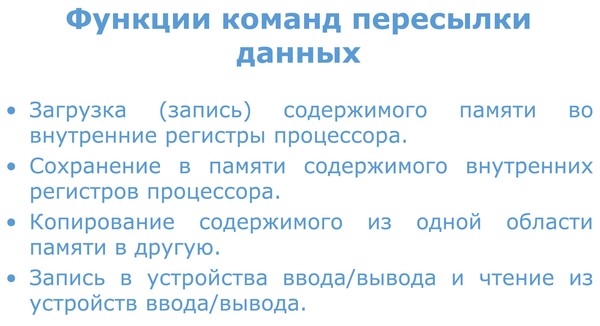

Команды пересылки данных обеспечивают обмен информацией между регистрами микропроцессора, а также внешние обмены данными при передаче в процессор из памяти или устройства ввода и из процессора в память или устройство вывода. В этих командах обычно указывается направление передачи, источник и (или) приёмник данных.

Например, в языке ассемблера к командам этой группы можно отнести команду пересылки MOV, команду загрузки LOAD, команды записи в порт и чтения из порта УВВ, IN и OUT, соответственно. Также сюда часто включают команды помещения данных в стек PUSH и извлечения данных из стека POP.

mov ax,4; Переслать в регистр ax значение 4

mov al,a; Переслать в регистр al значение по адресу a

mov a,al; Переслать в ячейку по адресу a содержимое регистра al

in al,61h; Считать в регистр al значение порта 61 h

out 61h,al; Вывести в порт 61 h содержимое регистра al

add ax,4; Сложить содержимое регистра ax со значением 4

sub al,a; Вычесть из регистр al значение по адресу a

mul a; Умножить значение по адресу a на содержимое регистра al

or al,00000001b; Установить в регистре al значение нулевого ; бита в 1

and ah,0; Сбросить все биты регистра al в 0

Команды передачи управления используются для изменения последовательности выполнения команд при наличии программных ветвлений: команд условных и безусловного (JMP) переходов, обращении к подпрограммам (CALL) и выхода из них (RETURN). Команды условных переходов реализуют передачи управления в зависимости от значения флагов в регистре PSW. С их помощью процессор выполняет одну из возможных ветвей продолжения программы. Обычно в системе команд имеется несколько команд условных переходов.

jmp m1; Перейти на команду с адресом m 1

m1: mul a; Умножить значение по адресу a на содержимое ;регистра al

В современных процессорах системы команд наряду с традиционными командами, перечисленными выше, содержат в своём составе группы команд, расширяющие функциональные возможности микропроцессора по обработке информации, управлению его работой, а также обеспечивающие реализацию многозадачного защищённого режима работы.

В системы команд конкретных процессоров могут входить команды, не вписывающиеся в предложенную классификацию. Подобные команды не отражают общих принципов построения программ и рассматриваются как дополнительные.

Выполнение команды (машинной операции) разделено на более мелкие этапы – микрооперации (микрокоманды), во время которых выполняются определённые элементарные действия. Конкретный состав микроопераций определяется системой команд и логической структурой ВМ. Последовательность микрокоманд, реализующих данную операцию (команду), образует микропрограмму операции. Интервал времени, в течение которого выполняется одна или одновременно несколько микроопераций, называется машинным тактом. Границы тактов задаются синхросигналами, которые вырабатываются генератором синхросигналов.

В общем случае, команда микропроцессора содержит две части: операционную и адресную (рис. 4).

| Операционная часть |

| Адресная часть |

| A1 |

| A2 |

| A3 |

| A4 |

| Адреса операндов |

| Адрес результата |

| Адрес след. команды |

| Код операции |

| КОП |

Рис. 4. Прямая адресация

Соглашение о распределении разрядов между этими частями команды и способе кодирования информации определяет структуру (формат) команды.

В операционной части команды содержится код операции (КОП), обеспечивающий кодирование операций (где n – число двоичных разрядов, отведённых под операционную часть команды) и определяющий, какие устройства в процессоре или вне его при этом будут задействованы.

В k -разрядной адресной части команды содержится информация об адресах операндов, участвующих в выполнении операции. В общем случае адресная часть команды должна содержать четыре адресных поля A 1, A 2, A 3, A 4. Они предназначены для задания адресов операндов (A 1, A 2), адреса результата (A 3) и адреса следующей команды (A 4). В качестве адресов A 1,…, A 3 могут использоваться адреса ячеек оперативной памяти и адреса регистров микропроцессорной памяти, в качестве адреса A 4 – только адреса ячеек оперативной памяти.

При использовании полного набора адресов формат команды оказывается громоздким. Следует отметить, что не для всех операций необходим полный набор адресов A 1 – A 4. В зависимости от указываемого числа адресов команды подразделяются на 0-адресные или безадресные (например, NOP – ничего не делать), 1-адресные (например, PUSH AX – поместить содержимое регистра AX в вершину стека), 2-адресные (например, ADD AH,AL – сложить содержимое регистров AH и AL), 3-адресные (тогда операция сложения, например, могла бы выглядеть следующим образом: ADD AH,AL,BX – сложить содержимое регистров AH и AL с сохранением результата в регистре BX) и 4-адресные (операция сложения могла быть записана, например, так ADD AH,AL,BX, 0020 – сложить содержимое регистров AH и AL с сохранением результата в регистре BX и последующей загрузкой команды по смещению 0020 в сегменте кода).

Практически во всех микропроцессорах адрес A 4 исключён. Это обусловлено тем, что большинство команд относятся к линейным участкам алгоритмов, и такие команды могут быть размещены в ячейках памяти с последовательно возрастающими адресами. В этом случае для получения адреса следующей команды к начальному адресу сегмента кода достаточно добавить смещение этой команды в сегменте кода, что удобно реализовать с помощью указателя команд (IP). Такой способ адресации команд называется естественным, а реализующие его процессоры называются процессорами с естественным способом адресации команд. При нарушении естественного порядка следования команд (ветвлениях, циклах) используются специальные команды передачи управления, в которых содержится адрес перехода, но не используются адреса операндов. Процессоры, в адресном поле команд которых используется адрес A 4, называются процессорами с принудительным способом адресации команд.

Использование адреса результата A 3 во многих случаях также оказывается избыточным. Это обосновывается тем, что результат арифметических и логических операций над двумя операндами обычно может быть помещён на место одного из операндов, который в дальнейшем, скорее всего, использоваться не будет. При этом в 2-адресных командах в адресное поле необходимо вводить дополнительные разряды, показывающие, кто из них является источником, а кто – приёмником информации. В процессорах с аккумуляторной архитектурой число адресов в адресной части команды уменьшено до одного. В них один из операндов, размещённых в аккумуляторе, неявно задаётся кодом команды, и результат помещается в аккумулятор.

В безадресных командах осуществляется неявное задание операнда. К таким командам относятся команды управления процессором (например, пуска, останова и т.д.) и команды для работы со стеком (операнд, адресуемый указателем SP, неявно задаётся кодом команды). Безадресные команды имеют предельно сокращённый формат, но не могут самостоятельно образовать функционально полную систему команд и поэтому применяются только вместе с адресными.

Формат команд влияет на время решения задач, затраты памяти, сложность процессора и зависит от класса решаемых задач. В частности, для научно- технических расчётов, в которых большой объём занимают многошаговые вычисления, более эффективными оказываются 1-адресные команды, а при использовании стекового процессора – и безадресные команды. Для задач управления, где большую долю составляют пересылки и логические операции, эффективными являются 2-адресные команды. Исходя из сказанного выше, следует отметить, что в современных процессорах обычно используются безадресные, 1-адресные и 2-адресные команды. 3-адресные команды используются крайне редко, а 4-адресные не используются совсем.

Для процессора Intel 8086 используются следующие форматы команд:

В зависимости от структуры данных и их местонахождении доступ к ним может осуществляться различными способами. Рассмотрим режимы адресации данных для микропроцессора Intel 8086.

Каждая команда должна содержать сведения, необходимые для ее выполнения. Сведения кодируются. Для кодировки каждой группы сведений выделяется свое поле. Совокупность полей, содержащих необходимые сведения для выполнения требуемой операции, называют форматом команды. В формате команды должны быть определены:

● функциональное назначение операции в виде кода операции;

● адреса источников данных. В общем случае должны быть указаны адреса двух операндов;

● адрес места расположения результата;

● адрес следующей команды.

Способы уменьшения формата команды.

Рассмотрим гипотетическую ситуацию. Допустим, что в формате команды:

● поле кода операций (КО) занимает 4 разряда, что позволяет закодировать 2 4 = 16 операций;

● под адреса двух операндов–источников, адрес места расположения результата, адрес следующей команды выделены поля А O 1, А O 2, АР, АСК (рис. 2.7.1) по 12 разрядов, что позволяет в каждом случае адресовать 2 12 = 4К ячеек памяти.

Как видно из рис. 2.7.1, несмотря на скромные возможности команды, ее общая длина составляет достаточно большое число (52) бит. Для сокращения количества разрядов команды часть информации должна быть задана неявно и не должна зависеть от особенностей конкретной команды.

Наиболее употребительными являются следующие способы сокращения длины кода команды:

● использование специально предусмотренных для адресации регистров: программного счетчика, указателя стека и др. Например, при выполнении команд с последовательно возрастающими адресами программный счетчик автоматически считывает из памяти следующую команду. В этом случае в формате команды отсутствует поле адреса следующей команды;

● использование неявных способов адресации. Например, при использовании неявной регистровой адресации адрес следующей команды или операнда хранится в регистре, код которого содержит значительно меньшее число разрядов, чем код исполнительного адреса;

● совмещение источника одного из операндов с приемником результата. В этом случае в формате команды исключается поле адреса результата;

● использование команд с укороченной адресацией, т. е. части адресного пространства памяти;

● использование для некоторой группы операций одного регистра. Наиболее часто для этой цели используется аккумулятор. В операциях с аккумулятором не требуется его кодировка. Например, команда ADD

В выполняет операцию сложение содержимого регистра В с аккумулятором А и в него же помещает результат. Такая команда является одноадресной. Ее формат состоит из двух полей: кода операции и адреса операнда. Однако одноадресные команды требуют дополнительных команд для предварительной загрузки операндов в аккумулятор и последующего размещения результатов в памяти;

● использование нескольких аккумуляторов (Motorola 6800, National РАСЕ, Signetic 2650). В этом случае каждая команда имеет два адреса, однако адрес источника и места назначения может быть задан другим аккумулятором. Следует отметить, что в одних процессорах все команды имеют одинаковую длину, в других — разную длину. Одинаковая длина всех команд упрощает декодирование, однако требует большего пространства, поскольку все команды должны быть такой же длины, как самая длинная. Команды могут быть короче слова, равными слову или длиннее слова. В процессорах с неймановской архитектурой команды и данные имеют одинаковую длину и поступают в процессор по шине данных. Поэтому для отличия команд отданных в процессоре предусмотрены средства, обеспечивающие:

● засылку команд (первого байта) в регистр команд с дальнейшей их дешифрацией для активизации устройства управления;

● поступление данных (последующих байт) в аккумулятор или другие регистры для обработки в АЛУ.

Форматы команд некоторых процессоров.

Рассмотрим в общих чертах форматы команд 8–разрядного (8080) и 16–разрядного (8086) процессоров. Длина команды кратна байту и может составлять один, два и более байт.

Достаточно простые форматы имеют команды процессора 8080 (рис. 2.7.2). Длина команд составляет от 1 до 3 байт. Код операции всегда размещается в первом байте команды. Второй и третий байты отводятся под непосредственные данные, адрес порта или ячейки памяти. В командах допускается явное задание только одного адреса памяти. Поэтому система команд процессора 8080 относится к классу одноадресных.

На рис. 2.7.3 изображены форматы команд процессора 8086. Длина команд составляет от 1 до 6 байт.

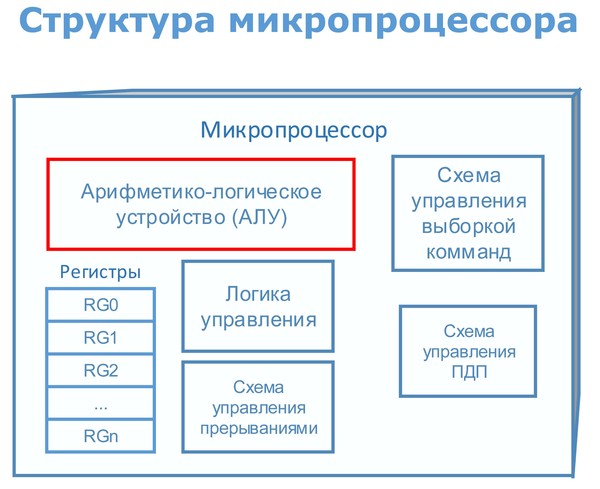

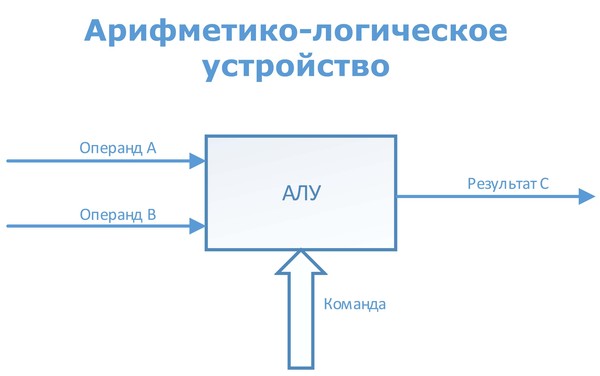

Микропроцессор выполняет программу, которая представляет собой последовательность команд. Каждая команда – это определенное действие, которое выполняет арифметико-логическое устройство.

Внутри АЛУ находятся блоки, каждый из которых может выполнять

одно или несколько действий, какой именно блок будет использоваться – определяется командой. Рассмотрим подробнее, каким образом это происходит.

Многие могут подумать, что сейчас, когда создание программ осуществляется на языках высокого уровня, совсем не обязательно знать, как выполняются отдельные команды в микропроцессоре. Однако, понимания принципов функционирования микропроцессора позволит создавать программы, которые будут максимально раскрывать потенциал современного микропроцессора и станет понятно, почему использование одних конструкций в программе предпочтительно, а других – нежелательно. Основная функция АЛУ – выполнение арифметических операций. На вход арифметико-логического устройства поступают некие числа и команда, которая определяет, какое действие будет производиться с этими числами. Результат, полученный после выполнения этого действия – тоже число – подается на выход.

Данные, с которыми работает АЛУ – операнды и результат – хранятся в одном из блоков

памяти. Работа с памятью – также функция АЛУ. Скорость обмена данными с внешними блоками памяти очень низкая по сравнению со скоростью работы АЛУ. Поэтому внутри МП предусмотрены ячейки памяти – регистры общего назначения, скорость чтения и записи в которые совпадает со скоростью работы АЛУ. В качестве операндов обычно может использовать только данные, которые хранятся во внутренних регистрах МК общего назначения. Результат также будет помещен в один из этих регистров. В команде обычно указано, из какого регистра берутся входные операнды и в какой регистр должен быть записан результат. Для работы с данными АЛУ сначала копирует данные из памяти в регистры, для чего предусмотрены отдельные команды.Все данные, необходимые для работы в ближайшее время, должны быть скопированы из памяти в регистры. А если получен результат, который не будет использоваться в ближайшее время, он может быть скопирован в память. Этот алгоритм позволяет существенно ускорить работу процессора. Хранить все данные в регистрах невозможно, т.к. объем регистров значительно меньше объема оперативной памяти, т.к. сделать быструю память большого объёма на одном кристалле с АЛУ технологически сложно и дорого.

По функциональному назначению команды можно разделить на четыре группы: команды

пересылки данных, арифметические команды, логические команды и команды переходов.

Команды пересылки данных осуществляют загрузку данных из памяти во внутренние регистры процессора, сохранение в памяти содержимого регистров, копирование данных из одной области памяти в другую и обмен данными с устройствами ввода-вывода

Группа арифметических команд реализует большинство арифметических операций –сложение, вычитание, умножение, деление, возведение в степень и другие. Операции над числами с фиксированной запятой (т.е. целыми числами) и над числами с плавающей запятой осуществляются разными командами, т.к. внутри АЛУ эти операции будут выполняться в разных блоках. Также к арифметическим командам относят команду очистка (т.е. запись нулевого значения в некоторый регистр), команды инкремента и декремента – т.е. увеличения или уменьшения значения на 1 и команда сравнения. Команда сравнения в результате выдает 0, если число отрицательно и 1, если число положительно

Логические команды реализуют логические операции – и, или, не, сложение по модулю 2, битовые сдвиги, установку и очистку битов регистра состояния процессора. Команды переходов могут менять порядок выполнения программы. Обычный порядок – это последовательное выполнение команд, одна за другой. В специальном регистре микропроцессора записано значение счетчика команд и при последовательном выполнении значение счетчика каждый раз увеличивается на 1

Но в некоторых случаях необходимо начать выполнять команды, которые записаны в другом месте программы. Для этого применяются команды перехода – в них указано новое значение счетчика команда, т.е. номер команды, которая должна будет выполняться на следующем такте

По функциональному признаку все команды процессора можно разделить на следующие группы:

1) команды пересылки данных и ввода – вывода;

2) команды арифметических и поразрядных логических операций;

3) команды передачи управления.

Команды пересылки данных обеспечивают обмен информацией между регистрами микропроцессора, а также внешние обмены данными при передаче в процессор из памяти или устройства ввода и из процессора в память или устройство вывода. В этих командах обычно указывается направление передачи, источник и (или) приёмник данных.

Например, в языке ассемблера к командам этой группы можно отнести команду пересылки MOV, команду загрузки LOAD, команды записи в порт и чтения из порта УВВ, IN и OUT, соответственно. Также сюда часто включают команды помещения данных в стек PUSH и извлечения данных из стека POP.

mov ax,4; Переслать в регистр ax значение 4

mov al,a; Переслать в регистр al значение по адресу a

mov a,al; Переслать в ячейку по адресу a содержимое регистра al

in al,61h; Считать в регистр al значение порта 61 h

out 61h,al; Вывести в порт 61 h содержимое регистра al

add ax,4; Сложить содержимое регистра ax со значением 4

sub al,a; Вычесть из регистр al значение по адресу a

mul a; Умножить значение по адресу a на содержимое регистра al

or al,00000001b; Установить в регистре al значение нулевого ; бита в 1

and ah,0; Сбросить все биты регистра al в 0

Команды передачи управления используются для изменения последовательности выполнения команд при наличии программных ветвлений: команд условных и безусловного (JMP) переходов, обращении к подпрограммам (CALL) и выхода из них (RETURN). Команды условных переходов реализуют передачи управления в зависимости от значения флагов в регистре PSW. С их помощью процессор выполняет одну из возможных ветвей продолжения программы. Обычно в системе команд имеется несколько команд условных переходов.

jmp m1; Перейти на команду с адресом m 1

m1: mul a; Умножить значение по адресу a на содержимое ;регистра al

В современных процессорах системы команд наряду с традиционными командами, перечисленными выше, содержат в своём составе группы команд, расширяющие функциональные возможности микропроцессора по обработке информации, управлению его работой, а также обеспечивающие реализацию многозадачного защищённого режима работы.

В системы команд конкретных процессоров могут входить команды, не вписывающиеся в предложенную классификацию. Подобные команды не отражают общих принципов построения программ и рассматриваются как дополнительные.

Выполнение команды (машинной операции) разделено на более мелкие этапы – микрооперации (микрокоманды), во время которых выполняются определённые элементарные действия. Конкретный состав микроопераций определяется системой команд и логической структурой ВМ. Последовательность микрокоманд, реализующих данную операцию (команду), образует микропрограмму операции. Интервал времени, в течение которого выполняется одна или одновременно несколько микроопераций, называется машинным тактом. Границы тактов задаются синхросигналами, которые вырабатываются генератором синхросигналов.

В общем случае, команда микропроцессора содержит две части: операционную и адресную (рис. 4).

| Операционная часть |

| Адресная часть |

| A1 |

| A2 |

| A3 |

| A4 |

| Адреса операндов |

| Адрес результата |

| Адрес след. команды |

| Код операции |

| КОП |

Рис. 4. Прямая адресация

Соглашение о распределении разрядов между этими частями команды и способе кодирования информации определяет структуру (формат) команды.

В операционной части команды содержится код операции (КОП), обеспечивающий кодирование операций (где n – число двоичных разрядов, отведённых под операционную часть команды) и определяющий, какие устройства в процессоре или вне его при этом будут задействованы.

В k -разрядной адресной части команды содержится информация об адресах операндов, участвующих в выполнении операции. В общем случае адресная часть команды должна содержать четыре адресных поля A 1, A 2, A 3, A 4. Они предназначены для задания адресов операндов (A 1, A 2), адреса результата (A 3) и адреса следующей команды (A 4). В качестве адресов A 1,…, A 3 могут использоваться адреса ячеек оперативной памяти и адреса регистров микропроцессорной памяти, в качестве адреса A 4 – только адреса ячеек оперативной памяти.

При использовании полного набора адресов формат команды оказывается громоздким. Следует отметить, что не для всех операций необходим полный набор адресов A 1 – A 4. В зависимости от указываемого числа адресов команды подразделяются на 0-адресные или безадресные (например, NOP – ничего не делать), 1-адресные (например, PUSH AX – поместить содержимое регистра AX в вершину стека), 2-адресные (например, ADD AH,AL – сложить содержимое регистров AH и AL), 3-адресные (тогда операция сложения, например, могла бы выглядеть следующим образом: ADD AH,AL,BX – сложить содержимое регистров AH и AL с сохранением результата в регистре BX) и 4-адресные (операция сложения могла быть записана, например, так ADD AH,AL,BX, 0020 – сложить содержимое регистров AH и AL с сохранением результата в регистре BX и последующей загрузкой команды по смещению 0020 в сегменте кода).

Практически во всех микропроцессорах адрес A 4 исключён. Это обусловлено тем, что большинство команд относятся к линейным участкам алгоритмов, и такие команды могут быть размещены в ячейках памяти с последовательно возрастающими адресами. В этом случае для получения адреса следующей команды к начальному адресу сегмента кода достаточно добавить смещение этой команды в сегменте кода, что удобно реализовать с помощью указателя команд (IP). Такой способ адресации команд называется естественным, а реализующие его процессоры называются процессорами с естественным способом адресации команд. При нарушении естественного порядка следования команд (ветвлениях, циклах) используются специальные команды передачи управления, в которых содержится адрес перехода, но не используются адреса операндов. Процессоры, в адресном поле команд которых используется адрес A 4, называются процессорами с принудительным способом адресации команд.

Использование адреса результата A 3 во многих случаях также оказывается избыточным. Это обосновывается тем, что результат арифметических и логических операций над двумя операндами обычно может быть помещён на место одного из операндов, который в дальнейшем, скорее всего, использоваться не будет. При этом в 2-адресных командах в адресное поле необходимо вводить дополнительные разряды, показывающие, кто из них является источником, а кто – приёмником информации. В процессорах с аккумуляторной архитектурой число адресов в адресной части команды уменьшено до одного. В них один из операндов, размещённых в аккумуляторе, неявно задаётся кодом команды, и результат помещается в аккумулятор.

В безадресных командах осуществляется неявное задание операнда. К таким командам относятся команды управления процессором (например, пуска, останова и т.д.) и команды для работы со стеком (операнд, адресуемый указателем SP, неявно задаётся кодом команды). Безадресные команды имеют предельно сокращённый формат, но не могут самостоятельно образовать функционально полную систему команд и поэтому применяются только вместе с адресными.

Формат команд влияет на время решения задач, затраты памяти, сложность процессора и зависит от класса решаемых задач. В частности, для научно- технических расчётов, в которых большой объём занимают многошаговые вычисления, более эффективными оказываются 1-адресные команды, а при использовании стекового процессора – и безадресные команды. Для задач управления, где большую долю составляют пересылки и логические операции, эффективными являются 2-адресные команды. Исходя из сказанного выше, следует отметить, что в современных процессорах обычно используются безадресные, 1-адресные и 2-адресные команды. 3-адресные команды используются крайне редко, а 4-адресные не используются совсем.

Для процессора Intel 8086 используются следующие форматы команд:

В зависимости от структуры данных и их местонахождении доступ к ним может осуществляться различными способами. Рассмотрим режимы адресации данных для микропроцессора Intel 8086.

Читайте также: