Что делает внешнее устройство при получении от процессора сигнала предоставления прерывания

Обновлено: 02.07.2024

Аппаратная поддержка прерываний имеет свои особенности, зависящие от типа процессора и других аппаратных компонентов, передающих сигнал запроса прерывания от внешнего устройства к процессору (таких, как контроллер внешнего устройства, шины подключения внешних устройств, контроллер прерываний, являющийся посредником между сигналами шины и сигналами процессора). Особенности аппаратной реализации прерываний оказывают влияние на средства программной поддержки прерываний, работающие в составе ОС.

Существуют два основных способа, с помощью которых шины выполняют прерывания: векторный (vectored) и опрашиваемый (polled). В обоих способах процессору предоставляется информация об уровне приоритета прерывания на шине подключения внешних устройств. В случае векторных прерываний в процессор передается также информация о начальном адресе программы обработки возникшего прерывания — обработчика прерываний.

Векторный способ.

Устройствам, которые используют векторные прерывания, назначается вектор прерываний. Он представляет собой электрический сигнал, выставляемый на соответствующие шины процессора и несущий в себе информацию об определенном, закрепленном за данным устройством номере, который идентифицирует соответствующий обработчик прерываний. Этот вектор может быть фиксированным, конфигурируемым (например, с использованием переключателей) или программируемым. ОС может предусматривать процедуру регистрации вектора обработки прерываний для определенного устройства, которая связывает некоторую подпрограмму обработки прерываний с определенным вектором. При получении сигнала запроса прерывания процессор выполняет специальный цикл подтверждения прерывания, в котором устройство должно идентифицировать себя. В течение этого цикла устройство отвечает, выставляя на шину вектор прерываний. Затем процессор использует этот вектор для нахождения обработчика данного прерывания. Примером шины подключения внешних устройств, которая поддерживает векторные прерывания, является шина VMEbus.

При использовании опрашиваемых прерываний процессор получает от запросившего прерывание устройства только информацию об уровне приоритета прерывания (например, номере IRQ на шине ISA или номере IPL на шине SBus компьютеров SPARC). С каждым уровнем прерываний может быть связано несколько устройств и соответственно несколько программ — обработчиков прерываний. При возникновении прерывания процессор должен определить, какое устройство из тех, которые связаны с данным уровнем прерываний, действительно запросило прерывание. Это достигается вызовом всех обработчиков прерываний для данного уровня приоритета, пока один из обработчиков не подтвердит, что прерывание пришло от обслуживаемого им устройства. Если же с каждым уровнем прерываний связано только одно устройство, то определение нужной программы обработки прерывания происходит немедленно, как и при векторном прерывании. Опрашиваемые прерывания поддерживают шины ISA, EISA, MCA, PCI и Sbus.

Механизм прерываний некоторой аппаратной платформы может сочетать векторный и опрашиваемый типы прерываний. Типичным примером такой реализации является платформа персональных компьютеров на основе процессоров Intel Pentium. Шины PCI, ISA, EISA или MCA, используемые в этой платформе в качестве шин подключения внешних устройств, поддерживают механизм опрашиваемых прерываний. Контроллеры периферийных устройств выставляют на шину не вектор, а сигнал запроса прерывания определенного уровня IRQ. Однако в процессоре Pentium система прерываний является векторной.

Приоритезация и маскирование прерываний.

Механизм прерываний чаще всего поддерживает приоритезацию и маскирование прерываний. Приоритезация означает, что все источники прерываний делятся на классы и каждому классу назначается свой уровень приоритета запроса на прерывание. Приоритеты могут обслуживаться как относительные и абсолютные:

схема с относительными приоритетами заключается в том, что при одновременном поступлении запросов прерываний из разных классов выбирается запрос, имеющий высший приоритет. Однако в дальнейшем при обслуживании этого запроса процедура обработки прерывания уже не откладывается даже в том случае, когда появляются более приоритетные запросы — решение о выборе нового запроса принимается только в момент завершения обслуживания очередного прерывания.

схема приоритезации с абсолютными приоритетами - более приоритетным прерываниям разрешается приостанавливать работу процедур обслуживания менее приоритетных прерываний.

Если процессор (или компьютер, когда поддержка приоритезации прерываний вынесена во внешний по отношению к процессору блок) работает по схеме с абсолютными приоритетами, то он поддерживает в одном из своих внутренних регистров переменную, фиксирующую уровень приоритета обслуживаемого в данный момент прерывания. При поступлении запроса из определенного класса его приоритет сравнивается с текущим приоритетом процессора, и если приоритет запроса выше, то текущая процедура обработки прерываний вытесняется, а по завершении обслуживания нового прерывания происходит возврат к прерванной процедуре.

Упорядоченное обслуживание запросов прерываний наряду со схемами приоритетной обработки запросов может выполняться механизмом маскирования запросов. Собственно говоря, в описанной схеме абсолютных приоритетов выполняется маскирование — при обслуживании некоторого запроса все запросы с равным или более низким приоритетом маскируются, то есть не обслуживаются. Схема маскирования предполагает возможность временного маскирования прерываний любого класса независимо от уровня приоритета.

Обработка прерываний

Обобщенно последовательность действий аппаратных и программных средств по обработке прерывания можно описать следующим образом.

При возникновении сигнала (для аппаратных прерываний) или условия (для внутренних прерываний) прерывания происходит первичное аппаратное распознавание типа прерывания. Если прерывания данного типа в настоящий момент запрещены (приоритетной схемой или механизмом маскирования), то процессор продолжает поддерживать естественный ход выполнения команд. В противном случае в зависимости от поступившей в процессор информации (уровень прерывания, вектор прерывания или тип условия внутреннего прерывания) происходит автоматический вызов процедуры обработки прерывания, адрес которой находится в специальной таблице операционной системы, размещаемой либо в регистрах процессора, либо в определенном месте оперативной памяти.

Автоматически сохраняется некоторая часть контекста прерванного потока, которая позволит ядру возобновить исполнение потока процесса после обработки прерывания. В это подмножество обычно включаются значения счетчика команд, слова состояния машины, хранящего признаки основных режимов работы процессора (пример такого слова — регистр EFLAGS в Intel Pentium), а также нескольких регистров общего назначения, которые требуются программе обработки прерывания. Может быть сохранен и полный контекст процесса, если ОС обслуживает данное прерывание со сменой процесса. Однако в общем случае это не обязательно, часто обработка прерываний выполняется без вытеснения текущего процесса.

Одновременно с загрузкой адреса процедуры обработки прерываний в счетчик команд может автоматически выполняться загрузка нового значения слова состояния машины (или другой системной структуры, например селектора кодового сегмента в процессоре Pentium), которое определяет режимы работы процессора при обработке прерывания, в том числе работу в привилегированном режиме. В некоторых моделях процессоров переход в привилегированный режим за счет смены состояния машины при обработке прерывания является единственным способом смены режима. Прерывания практически во всех мультипрограммных ОС обрабатываются в привилегированном режиме модулями ядра, так как при этом обычно нужно выполнить ряд критических операций, от которых зависит жизнеспособность системы, — управлять внешними устройствами, перепланировать потоки и т. п.

Временно запрещаются прерывания данного типа, чтобы не образовалась очередь вложенных друг в друга потоков одной и той же процедуры. Детали выполнения этой операции зависят от особенностей аппаратной платформы, например может использоваться механизм маскирования прерываний. Многие процессоры автоматически устанавливают признак запрета прерываний в начале цикла обработки прерывания, в противном случае это делает программа обработки прерываний.

После того как прерывание обработано ядром операционной системы, прерванный контекст восстанавливается и работа потока возобновляется с прерванного места. Часть контекста восстанавливается аппаратно по команде возврата из прерываний (например, адрес следующей команды и слово состояния машины), а часть — программным способом, с помощью явных команд извлечения данных из стека. При возврате из прерывания блокировка повторных прерываний данного типа снимается.

Здесь мы разберем такие важные темы, как: обработка прерываний, векторы прерываний, программные прерывания, IRQ, в общем поговорим на темы прерывания.

Идея прерывания была предложена в середине 50-х годов и основная цель введения прерываний – реализация синхронного режима работы и реализация параллельной работы отдельных устройств ЭВМ.

Прерывания и обработка прерываний зависят от типа ЭВМ, поэтому их реализацию относят к машинно-зависимым свойствам операционных систем.

Прерывание (interrupt) – это сигнал, заставляющий ЭВМ менять обычный порядок выполнения команд процессором.

Возникновение подобных сигналов обусловлено такими событиями, как:

- завершение операций ввода-вывода.

- истечение заранее заданного интервала времени.

- попытка деления на нуль.

- сбой в работе аппаратного устройства и др.

Обработка прерывания

С каждым прерыванием связывают число, называемое номером типа прерывания или просто номером прерывания. Система умеет распознавать, какое прерывание, с каким номером оно произошло, и запускает соответствующую этому номеру программу обработки прерывания. Таким образом, при поступлении сигнала на прерывание происходит принудительная передача управления от выполняемой программы к системе, а через нее — к обработчику прерываний.

Например прерывание с номером 9 — прерывание от клавиатуры, которое генерируется при нажатии и при отжатии клавиши. Используется для чтения данных с клавиатуры. Обозначается в ОС как IRQ1, где IRQ – обозначение прерывания, а 1 – приоритет прерывания. Данные о запросах на прерывание можно проанализировать в диспетчере устройств:

Обработчик прерываний – программа обработки прерывания, являющаяся частью ОС, предназначенная для выполнения ответных действий на условие, вызвавшее прерывание.

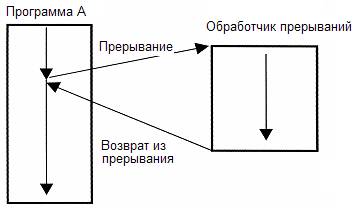

Предположим, что в момент поступления сигнала прерывания от некоторого источника программа А находится в решении. В результате управление автоматически передается обработчику прерываний. После завершения обработки управление может быть снова передано в ту точку программы А, где ее выполнение было прервано:

Векторы прерываний

Адреса программ, соответствующих различным прерываниям, собраны в таблицу, которая называется таблицей векторов прерываний.

Для микропроцессора требуется простой способ определения местоположения программы обработки прерывания и это осуществляется путем использования таблицы векторов прерываний.

Таблица векторов прерываний занимает первый килобайт оперативной памяти — адреса от 0000:0000 до 0000:03FF. Таблица состоит из 256 элементов — FAR-адресов обработчиков прерываний. Эти элементы называются векторами прерываний. В первом слове элемента таблицы записано смещение, а во втором — адрес сегмента обработчика прерывания. Векторами являются просто полные адреса памяти программы (в сегментированной форме), которая должна быть активизирована в случае возникновения прерывания.

Прерыванию с номером 0 соответствует адрес 0000:0000, прерыванию с номером 1 — 0000:0004 и т.д. Адрес такой состоит из пары 2-байтовых слов, поэтому каждый из векторов занимает четыре байта.

Можно просмотреть таблицу векторов прерываний в компьютере, если воспользоваться программой DEBUG. Используйте команду D для вывода содержимого начала памяти: D 0:0. Программа DEBUG покажет вам первые 128 байтов или 32 вектора, которые могут иметь вид наподобие следующего:

0000:0000 E8 4E 9A 01 00 00 00 00-C3 E2 00 F0 00 00 00 00

0000:0010 F0 01 70 00 54 FF 00 F0-05 18 00 F0 05 18 00 F0

0000:0020 2C 08 51 17 D0 0A 51 17-AD 08 54 08 E8 05 01 2F

0000:0030 FA 05 01 2F 05 18 00 F0-57 EF 00 F0 F0 01 70 00

0000:0040 90 13 C7 13 4D F8 00 F0-41 F8 00 F0 3E 0A 51 17

0000:0050 5C 00 B7 25 59 F8 00 F0-E2 0A 51 17 9C 00 B7 25

0000:0060 00 00 00 F6 8E 00 DE 09-6E FE 00 F0 F2 00 7B 09

0000:0070 27 08 51 17 A4 F0 00 F0-22 05 00 00 00 00 00 F0

Можно встретить три вида адресов в таблице векторов. Это могут быть адреса, указывающие на ROM-BIOS, которые можно идентифицировать шестнадцатеричной цифрой F, которая предшествует номеру сегмента. Это могут быть адреса, которые указывают на главную память (как в примере: 019A:4EE8). Эти адреса могут указывать на подпрограммы ДОС или на резидентную программу (например, SideKick или Prokey), либо они могут указывать на саму программу DEBUG (поскольку DEBUG должна временно управлять прерыванием). Также векторы могут состоять из одних нулей, когда прерывание с данным номером не обрабатывается в текущий момент.

Инициализация таблицы происходит частично BIOS после тестирования аппаратуры и перед началом загрузки операционной системой, частично при загрузке операционной системы.

Ниже приведено назначение некоторых векторов:

| № | Описание |

|---|---|

| 0 | Ошибка деления. Вызывается автоматически после выполнения команд DIV или IDIV, если в результате деления происходит переполнение (например, при делении на 0). |

| 2 | Аппаратное немаскируемое прерывание. Это прерывание может использоваться по-разному в разных машинах. Обычно вырабатывается при ошибке четности в оперативной памяти и при запросе прерывания от сопроцессора. |

| 5 | Печать копии экрана. Генерируется при нажатии на клавиатуре клавиши PrtScr. Обычно используется для печати образа экрана. |

| 8 | IRQ0 — прерывание интервального таймера, возникает 18,2 раза в секунду. |

| 9 | IRQ1 — прерывание от клавиатуры. Генерируется при нажатии и при отжатии клавиши. Используется для чтения данных от клавиатуры. |

| A | IRQ2 — используется для каскадирования аппаратных прерываний в машинах класса AT |

| B | IRQ3 — прерывание асинхронного порта COM2. |

| C | IRQ4 — прерывание асинхронного порта COM1. |

| D | IRQ5 — прерывание от контроллера жесткого диска для XT. |

| E | IRQ6 — прерывание генерируется контроллером флоппи-диска после завершения операции. |

| F | IRQ7 — прерывание принтера. Генерируется принтером, когда он готов к выполнению очередной операции. Многие адаптеры принтера не используют это прерывание. |

| 10 | Обслуживание видеоадаптера. |

| 11 | Определение конфигурации устройств в системе. |

| 12 | Определение размера оперативной памяти в системе. |

| 13 | Обслуживание дисковой системы. |

| 14 | Последовательный ввод/вывод. |

| 19 | Загрузка операционной системы. |

| 1A | Обслуживание часов. |

| 1B | Обработчик прерывания Ctrl-Break. |

| 70 | IRQ8 — прерывание от часов реального времени. |

| 71 | IRQ9 — прерывание от контроллера EGA. |

| 75 | IRQ13 — прерывание от математического сопроцессора. |

| 76 | IRQ14 — прерывание от контроллера жесткого диска. |

| 77 | IRQ15 — зарезервировано. |

IRQ0 — IRQ15 — это аппаратные прерывания.

Механизм обработки прерываний

При обработке каждого прерывания должна выполняться следующая последовательность действий:

- Восприятие запроса на прерывание: прием сигнала и идентификация прерывания.

- Запоминание состояния прерванного процесса: определяется значением счетчика команд (адресом следующей команды) и содержимым регистров процессора.

- Передача управления прерывающей программе (в счетчик команд заносится начальный адрес подпрограммы обработки прерываний, а в соответствующие регистры – информация из слова состояния процессора).

- Обработка прерывания.

- Восстановление прерванного процесса и возврат в прерванную программу.

Главные функции механизма прерывания:

- распознавание или классификация прерываний.

- передача управления соответственно обработчику прерываний.

- корректное возвращение к прерванной программе (перед передачей управления обработчику прерываний содержимое регистров процессора запоминается либо в памяти с прямым доступом либо в системном стеке).

Типы прерываний

Прерывания, возникающие при работе вычислительной системы, можно разделить на 4 группы:

Аппаратные прерывания вызываются физическими устройствами и возникают по отношению к программе асинхронно, т.е. в общем случае невозможно предсказать, когда и по какой причине программа будет прервана.

Аппаратные прерывания не координируются c работой программного обеспечения. Когда вызывается прерывание, то процессор оставляет свою работу, выполняет прерывание, a затем возвращается на прежнее место.

Внешние прерывания возникают по сигналу какого-либо внешнего устройства например:

- Прерывание, которое информирует систему о том, что требуемый сектор диска уже прочитан, его содержимое доступно программе.

- Прерывание, которое информирует систему о том, что завершилась печать символа на принтере и необходимо выдать следующий символ.

- Прерывания по нарушению питания.

- Нормальное завершение некоторой операции ввода-вывода (нажатие клавиши на клавиатуре).

- Прерывание по таймеру.

Прерывание по таймеру вызывается интервальным таймером. Этот таймер содержит регистр, которому может быть присвоено определенное начальное значение посредством специальной привилегированной команды. Значение этого регистра автоматически уменьшается на 1 по истечении каждой миллисекунды времени. Когда это значение становятся равным нулю, происходит прерывание по таймеру. Подобный интервальный таймер используется операционной системой для определения времени, в течение которого программа пользователя может оставаться под управлением машины.

Маскируемые и немаскируемые внешние прерывания

Существуют два специальных внешних сигнала среди входных сигналов процессора, при помощи которых можно прервать выполнение текущей программы и тем самым переключить работу центрального процессора. Это сигналы NMI (Non Mascable Interrupt, немаскируемое прерывани) INTR (interrupt request, запрос на прерывание).

Соответственно внешние прерывания подразделяются на два вида: немаскируемые и маскируемые.

Часто при выполнении критических участков программ, для того чтобы гарантировать выполнение определенной последовательности команд целиком, приходится запрещать прерывания (т.е. сделать систему нечувствительной ко всем или отдельным прерываниям). Это можно сделать командой CLI. Ее нужно поместить в начало критической последовательности команд, а в конце расположить команду STI, разрешающую процессору воспринимать прерывания. Команда CLI запрещает только маскируемые прерывания, немаскируемые всегда обрабатываются процессором.

Таким образом, наличие сигнала прерывания не обязательно должно вызывать прерывание исполняющейся программы. Процессор может обладать средствами защиты от прерываний: отключение системы прерываний, маскирование (запрет) отдельных сигналов прерываний. Прерывания, которые замаскировать нельзя — это немаскируемые прерывания.

Внутренние прерывания вызываются событиями, которые связаны с работой процессора и являются синхронными с его операциями, а именно прерывание происходит, когда:

- при нарушении адресации (в адресной части выполняемой команды указан запрещенный или несуществующий адрес, обращение к отсутствующему сегменту или странице при организации механизмов виртуальной памяти);

- при наличии в поле кода не задействованной двоичной комбинации.

- при делении на нуль.

- при переполнении или исчезновении порядка.

- при обнаружении ошибок четности, ошибок в работе различных устройств аппаратуры средствами контроля.

Программные прерывания

Программные прерывания в прямом смысле прерываниями не являются, поскольку представляют собой лишь специфический способ вызова процедур — не по адресу, а по номеру в таблице.

Механизм программных прерываний был специально введен для того, чтобы:

- переключение на системные программные модули происходило не просто как переход в подпрограмму, а точно таким же образом, как и обычные прерывания. Этим обеспечивается автоматическое переключение процессора в привилегированный режим с возможностью исполнения любых команд.

- использование программных прерываний приводит к более компактному коду программ по сравнению с использованием стандартных команд выполнения процедур.

Пример (программные прерывания):

- привилегированная команда в режиме пользователя.

- адрес вне диапазона.

- нарушение защиты памяти.

- арифметическое переполнение, отсутствует страница.

- нарушение защиты сегмента.

- выход за границу сегмента.

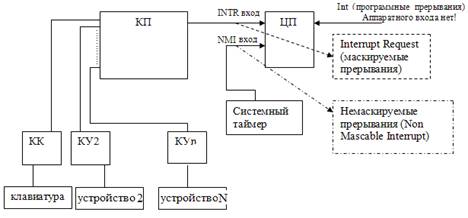

В упрощенном виде схему обработки различных видов прерываний можно представить следующим образом:

КП – контроллер прерываний, имеет несколько уровней (линий) для подключения контроллеров устройств (на схеме обозначены КУ). Возможно каскадное подключение контролеров, когда на один из его входов подключается еще одни контроллер прерываний. ЦП – центральный процессор.

Аппаратные прерывания вырабатываются устройствами компьютера, когда возникает необходимость их обслуживания. В отличие от программных прерываний, вызываемых запланировано самой прикладной программой, аппаратные прерывания всегда происходят асинхронно по отношению к выполняющимся программам. Кроме того, может возникнуть одновременно несколько прерываний. Выбор одного из них для обработки осуществляется на основе приоритетов, приписанных каждому типу прерывания.

Каждому прерыванию назначается свой уникальный приоритет. Если происходит одновременно несколько прерываний, то система отдает предпочтение самому высокоприоритетному, откладывая на время обработку остальных прерываний.

В случае о прерывании самой программы обработки прерывания говорят о вложенном прерывании. Уровни приоритетов обозначаются сокращенно IRQ0 — IRQ15 или IRQ0 – IRQ23 (в зависимости от микросхемой реализации).

Пpepывaнию вpeмeни cутoк дан мaкcимaльный пpиopитeт, пocкoльку ecли oнo будет пocтoяннo тepятьcя, то будут нeвepными пoкaзaния cиcтeмныx чacoв. Пpepывaниe от клaвиaтуpы вызывaeтcя при нaжaтии или oтпуcкaнии клавиши; oнo вызывaeт цепь coбытий, кoтopaя oбычнo зaкaнчивaeтcя тем, что код клавиши пoмeщaeтcя в буфep клaвиaтуpы (oткудa он зaтeм мoжeт быть пoлучeн пpoгpaммными пpepывaниями).

Ну и наконец реализация механизма обработки прерываний

В машине для каждого класса прерываний имеется соответствующая ему рабочая область прерываний. Например, имеется область, соответствующая прерыванию по таймеру. Когда происходит прерывание по таймеру, содержимое всех регистров сохраняется в этой области (например, пропустив первые несколько слов). Затем из этих пропущенных слов извлекаются заранее занесенные туда значения, которые перезаписываются в счетчик (указатель) команд машины и в слово состояния (или во флаговый регистр). Загрузка и сохранение регистров осуществляется аппаратными средствами машины автоматически.

Загрузка счетчика команд новым значением адреса автоматически вызывает передачу управления на соответствующую команду. Этот адрес, заранее сохраненный в рабочей области прерывания, представляет собой начальный адрес стандартной программы обработки прерываний по таймеру. Загрузка слова состояния также вызывает определенные изменения в состоянии процессора.

После выполнения в ответ на запрос на прерывание любого требуемого действия стандартная программа обработки прерываний выполняет команду загрузки состояния процессора, в результате чего управление передается прерванной программе. Происходит это следующим образом: команда загрузки состояния процессора вызывает загрузку сохраненного содержимого слова состояния, счетчика команд и других регистров из соответствующих слов области сохранения, начиная с адреса, указанного в команде. Это приводит к восстановлению содержимого регистров и состояния процессора, которые были в момент прерывания. Управление затем передается на команду, перед выполнением которой произошло прерывание.

Сохранение и восстановление состояния процессора и содержимого регистров называют операцией контекстного переключения.

У большинства машин имеется так называемое слово состояния, которое содержит часть информации, используемой при обработке прерываний. Одним из элементов этого слова (например, первый) является признак, определяющий, в каком режиме находится процессор: в пользовательском или супервизора.

Обычные программы находятся в пользовательском режиме (признак равен нулю). Когда происходит прерывание, новое загружаемое содержимое слово состояния имеет признак, равный 1, что автоматически переводит процессор в режим супервизора. В этом режиме становится возможным использование привилегированных команд. Перед тем, как значение слова состояния будет сохранено, в другом его элементе (например, втором) будет установлено значение, указывающее на причину прерывания:

- при программном прерывании отражается тип вызвавшего его условия, например деление на нуль.

- при прерывании по вводу-выводу заносится номер канала, вызвавший прерывание.

В третьем элементе указывается, выполняет ли процессор команды или простаивает. В четвертом элементе содержится указатель, идентифицирующий текущую выполняемую программу. В пятом элементе содержится маска прерываний, которая используется для контроля за разрешением прерываний (поле MASK).

Это поле используется, чтобы не допустить наступления прерываний определенного типа, пока первое из них не будет обработано. В MASK каждый бит соответствует некоторому классу прерываний. Если какой-то бит установлен в 1, то прерывания соответствующего класса разрешены, если в 0, то запрещены. В последнем случае говорят, что они маскированы (их также называют запрещеннымиили закрытыми). Однако маскированные прерывания не теряются, потому что сигнал, вызвавший прерывание, сохраняется аппаратурой. Временно задержанное таким способом прерывание называется отложенным. Когда (вследствие того, что значение MASK сброшено) прерывания соответствующего класса вновь разрешаются, сигнал опознается и происходит прерывание.

Маскирование прерываний находится под контролем операционной системы и зависит от значения MASK в слове состояния, которое заранее сохраняется в рабочей области каждого прерывания. Можно запретить все прерывания, установив все биты MASK в нуль. В действительности поступать подобным образом нет необходимости.

Взаимодействие с периферийным устройством подразумевает передачу информации в устройство, прием информации из устройства, настройка устройства или считывание состояния устройства. Для организации такого взаимодействия каждое устройство оснащено своими регистрами входных данных, выходных данных, состояния устройства и управления устройством.

К каждому регистру периферийного устройства процессор должен уметь обратиться. Простое периферийное устройство имеет в своем составе один или несколько таких регистров, содержимое которых можно прочитать или записать командами программы, исполняемой процессором. Сложные периферийные устройства могут содержать несколько десятков регистров.

В некоторых процессорах доступ к регистрам периферийных устройств осуществляется как ячейкам памяти: каждому регистру присвоен адрес в адресном пространстве памяти. Таким образом, для обращения к регистрам устройства используются те же команды, что и для доступа к ячейкам памяти. Для доступа к регистрам устройства, устройству выделяется фиксированный диапазон адресов.

В других процессорах регистры устройства имеют систему адресации не связанную с адресацией ячеек памяти: в этом случае для обращения к регистрам устройства в системе команд процессора имеются специальные команды ввода/ вывода. Доступные регистры периферийных устройств называют портами ввода-вывода.

Способы взаимодействия устройств

Обмен информацией вычислительной системе происходит по следующей схеме:

- одно устройство выполняет активную роль: чаще всего этим устройством является процессор;

- второе устройство является исполнителем

- используется принцип квитирования (запроса - ответа): каждый управляющий сигнал активного устройства, подтверждается сигналом исполнителя.

Можно выделить следующие способы взаимодействия устройств.

Ввод-вывод по прерываниям

Прямой доступ к памяти

Каждый способ придерживается указанной схемы обмена информацией; у каждого есть свои преимущества и недостатки. Рассмотрим подробнее каждый из них.

Программно-управляемый ввод-вывод

Хронологически это первый способ взаимодействия процессора с внешними устройствами, подключенными к общей шине.

Суть данного способа заключается в том, что процессор регулярно производится опрос присоединенных устройств, считывая регистр состояния устройства, чтобы понять, требуется ли устройству обмен.

Если текущему устройству обмен не требуется, процессор опрашивает следующее устройство. При неготовности внешних устройств к обмену, процессор продолжает выполнение своей задачи.

При готовности устройства к обмену (которое определяется битом в регистре состояния устройства) процессор, приостановив текущую задачу, переходит к выполнению программы ввод/вывода информации с данным устройством.

Сами внешние устройства в данном способе, просигнализировав о своем состоянии, в дальнейшем играют пассивную роль, принимая или отдавая данные процессору.

Плюсом данного способа является простота реализации. Недостатком - потери времени процессора на регулярное проведение опроса.

В современных системах данный способ не применяется.

Ввод-вывод по прерываниям

Ввод/вывод по прерываниям пришел на смену программно-управляемому вводу/выводу, который нерационально тратил время на опрос устройств, которые не готовы к обмену. Ввод/вывод по прерываниям предполагает, что процессор приостанавливает выполнение своей основной задачи только в том случае, если возникает запрос от самого внешнего устройства на обмен данными.

Алгоритм ввода/вывода по прерыванию заключается в следующем:

- Ввод/вывод инициируется внешним устройством, генерирующим сигнал прерывания.

- Процессор останавливает выполнение выполняемой программы и начинает обработку прерывания:

- Сохраняет адрес текущей выполняемой команды программы в стеке

- Сохранить в стеке текущее значение регистра состояния процессора (флагов)

- Определяет начальный адрес программы обработки прерывания по таблице векторов прерываний (Interrupt Descriptor Table, IDT)

- Выполняет программу обработки прерывания

- Восстанавливает прежнее состояние процессора, возвращая из стека регистр состояния процессора и адрес выполняемой команды прерванной программы.

Возможна ситуация, когда несколько устройств одновременно заявляют о намерении обмена с процессором (то есть инициируют прерывания). Для регулирования таких ситуаций прерываниям присваивается определённый приоритет; при одновременной подаче сигнала прерывания процессор будет обслуживать прерывание с более высоким уровнем приоритета. Одновременно обрабатывается одно прерывание.

Для регулирования вопросов арбитража прерываний в архитектуру вычислительной системы введен контроллер прерываний.

Контроллер прерываний принимает запросы на прерывания от различных устройств (на рисунке IRQ - Interrupt Request) и сохраняет факт запроса в специальном регистре – регистре запросов прерываний.

Контроллер прерываний имеет функцию маскирования прерываний: процессор может запретить реагировать на прерывания тех или иных устройств через настройки регистра маски. Каждый разряд регистра маски разрешает или запрещает прерывание от соответствующего разряду устройства.

В случае, если обратились несколько устройств, и всем им разрешены прерывания, система арбитража определяет, какой запрос процессор должен обслуживать первым.

Таким образом, контроллер принимает запросы на прерывания от всех присоединенных устройств, но дает запрос процессору на обслуживание единственного прерывания. Процессор, по мере завершения очередной выполняемой команды отвечает разрешением на обслуживание данного прерывания, и обслуживает его.

![]()

Ранее функции контроллера прерываний выполняли специализированные микросхемы на материнской плате; в настоящее время контроллер прерывания вынесен на Южный мост.

Для определения адреса программы, обрабатывающей прерывание, используется таблица векторов прерываний (Interrupt Descriptor Table, IDT). В таблице представлены номера некоторых (таблица приводится не полностью) прерываний.

Как видно из таблицы, некоторые прерывания генерируются самим процессором при определенных обстоятельства, например, ошибка деления на ноль. Прерывания от внешних устройств – это IRQ (Interrupt ReQuest) - аппаратные прерывания, которые генерируются устройствами, подключенными к компьютеру. К примеру, IRQ №0 генерируется PIT (таймер с программируемым интервалом), IRQ 1 генерируется при нажатии клавиши на клавиатуре.

Прямой доступ к памяти

Данный режим обмена данными предполагает взаимодействие между устройствами или между устройством и оперативной памятью без участия центрального процессора. То есть в данном режиме процессор не тратит свои ресурсы на обеспечение обмена.

Одно устройство принимает на себя активную роль, управляющего обменом, другое – пассивную, поддерживая обмен. При взаимодействии устройства с оперативной памятью пассивную роль принимает память.

Но для организации обмена устройствам нужно захватить шину, чтобы передавать по ней данные. При этом необходимо иметь гарантию, что в это время шина не используется процессором для решения задачи процессора, то есть надо организовать арбитраж шины. Арбитраж шины и управление обменом в режиме прямого доступа к памяти производится с помощью DMA-контроллера (Direct Memory Access).

Центральный процессор программирует контроллер прямого доступа к памяти, но не управляет обменом.

![]()

Взаимодействие устройства и памяти начинается с запроса устройства на доступ к памяти. Данный запрос принимается контроллером DMA и переадресуется процессору. В случае, если процессор не использует шину, он дает разрешение на захват шины устройством. Контроллер сообщает устройству, что обмен возможен, после чего производится обмен.

В настоящее время в вычислительных системах используется как прямой доступ к памяти, так и ввод/вывод по прерываниям.

Эволюция общей шины.

Можно выделить три поколения развития шин, обеспечивающих обмен между компонентами вычислительной системы.

Первое поколение

Первое поколение шин определяется как группа проводников, подключающей компьютерную память и периферию к процессору. Ввод-вывод осуществлялся в цикле ожидания готовности периферийного устройства процессором.

Шина была общая для всех устройств; всё оборудование на шине передавало информацию на одной скорости и использовало один источник синхросигнала. Увеличение скорости процессора автоматически увеличивало скорость работы всех устройств.

При установке любого устройства требовалось произвести настройку его параметров; специальными переключателями задавались

Усовершенствованием шин первого поколения было введение прерываний.

Примером шины первого поколения может служить шина ISA (Industry Standard Architecture), устанавливаемая на персональные компьютеры с 1981 года.

Разъем ISA состоял из 62 контактов:

· 20 -разрядная шина адреса,

· 6 линий прерывания,

· управляющие линии для чтения-записи памяти и устройств ввода/вывода,

· тактовые и синхронизирующие линии,

· 3 канала линий управления прямым доступом к памяти,

· линии управления регенерацией памяти,

· линия проверки канала,

ISA работала на частоте до 8 МГц и передавала данные со скоростью до 4 МБайт/с (при частоте работы процессоров ~4,7 МГц). Инициатором обмена могли выступать только процессор и контроллер DMA.

Усовершенствованием шины ISA было

· Удвоение разрядности данных (удвоение пропускной способности)

· Добавление четырех разряда адреса;

· Увеличилось число линий запросов прерываний (IRQ) и запросов прямого доступа к памяти (DMA).

- Любое подключенное к ней устройство могло инициировать операцию обмена данными

В 1993 году Intel и Microsoft разработали ISA PnP (Plug and Play), которая позволяла операционной системе самой определять назначаемое прерывание для устройства, тем самым исключая ручную настройку устанавливаемых устройств.

Второе поколение

Основным отличием шин второго поколения была изоляция процессора и памяти на собственной высокоскоростной шине. Между получившимися шинами был установлен специальный контроллер шин (bus controller).

Но все внешние устройства по-прежнему работали на одной скорости.

Во втором поколении шины разделили на внутренние (localbus) для подключения внутренних устройств, таких как видеоадаптеры и звуковые платы (примеры, PCI, PCI-Express), и внешние (externalbus) для подключения внешних устройств, например, сканеров (пример, USB, FireWire).

Данное разделение было несколько условно. Например, IDE является внешней шиной по своему предназначению, но почти всегда используется внутри компьютера.

Примером шины второго поколения может служить шина PCI (Peripheral Component Interconnect), выпущенная в 1992 году. Характеристики PCI:

· Параллельная передача данных

· Введение северного и южного моста, связь между ними

· Тактовая частота 33 МГц,

· Разрядность 32 или 64 бита

- Теоретически, пропускная способность шины 133 Мбайт/с, но пропускная способность шины делится между всеми устройствами

В то время тактовая частота процессоров составляла порядка ~ 50-60 МГц. Таким образом, PCI вполне соответствовала быстродействию системы в целом.

С увеличением частоты работы процессора и скорости работы всех прочих компонент, PCI развивалась. Основным направлением развития было увеличение пропускной способности за счет увеличения частоты шины.

В частности была реализация AGP (скоростного интерфейса видеоплаты) как частного случая PCI 2.0. при отсутствии арбитража интерфейса : к AGP допускалось подключение только одного устройства – видеоплаты.

Пределом PCI можно назвать PCI 2.1 66 МГц, обеспечивающей пропускную способность 266 Мбайт/с. Дальнейшее увеличение частоты было затруднительно в силу параллельной природы данного интерфейса. Кроме того, к этому моменту были созданы отдельные интерфейсы для процессора с памятью, для дисков внешней памяти. В настоящее время PCI используется только для модемов, сетевых и звуковых плат, но постепенно вытесняется PCI-Express.

Третье поколение

Шины третьего поколения (примером является внутренняя шина PCI-Express) архитектурно похожи на компьютерные сети, чем на изначальные идеи шин, что сопровождается большими накладными расходами, по сравнению с предыдущими поколениями.

Шины третьего поколения позволяют использовать как большие скорости, необходимые для памяти, видеокарт и межпроцессорного взаимодействия, так и небольшие при работе с медленными устройствами, например, приводами дисков.

Шины третьего поколения позволяют использовать шину нескольким устройствам одновременно.

Для достижения возможности одновременной передачи информации через одну шину различным устройствам на различных скоростях PCI-Express была реализована как пакетная сеть с топологией типа звезда. Устройства PCI-Express взаимодействуют между собой через среду , образованную коммутаторами. Каждое устройство напрямую связано с коммутатором соединением типа точка-точка.

Коммутатор (подробнее данное устройство описывается в рамках сетевых технологий) позволяет одновременно передавать через себя несколько потоков данных.

PCI-Express является последовательным интерфейсом, что позволяет передавать данные на высокой частоте. В первой версии PCI-Express при частоте передачи 2,5 ГГц по одной линии можно передавать данные на скорости 2500 МГц / 10 * 8 = 250 * 8 Мбит/сек = 250 Мбайт/сек для каждого устройства в одном направлении. Причиной деления на 10 является избыточное кодирование для передачи 8 бит данных десятью битами информации: при этом каждый байт перекодируется в соответствии с определенной схемой во избежание передачи подряд идущих нулей или единиц.

Но PCI-Express позволяет устройствам одновременно передавать в двух направлениях. Таким образом, максимальная пропускная способность удваивается.

Число линий PCI Express Пропускная способность в одном направлении Суммарная пропускная способность 250 Мб/сек 500 Мб/сек 500 Мб/сек 1 Гб/сек 1 Гб/сек 2 Гб/сек 2 Гб/сек 4 Гб/сек 4 Гб/сек 8 Гб/сек 8 Гб/сек 16 Гб/сек Шина PCI Express может использовать несколько таких последовательных соединений типа точка-точка, (для данного интерфейса они называются линиями), конструктивно соединенных в один интерфейс: x1 (одна линия), x2 (две линии), x4 (четыре линии), x8 (восемь линий), x12 (двенадцать линий), x16 (16 линий), x32 (32 линии). То есть соединение между картами PCI-Express может быть обеспечено как одной (1x), так и несколькими (2x, 4x, 8x, 12x, 16x, 32x) линиями.

Если слот PCI Express имеет приставку x16 (PCI Express x16), это означает, что он 16-канальный. В такой слот может быть установлена карта как PCI Express x1, так и PCI Express x16.

Шиной PCI Express поддерживается:

- горячая замена карт;

- гарантированная полоса пропускания (QoS);

- управление энергопотреблением;

- контроль целостности передаваемых данных.

Последующие версии PCI-Express удваивали частоту, и, соответственно, пропускную способность шины. В 2017 году вышла очередная версия - PCI Express 4.0.

Скорость компьютерных шин в настоящее время определяют в гигатранзакциях в секунду. За одну транзакцию передаётся один передаваемый элемент. Для расчёта реальной пропускной способности передаваемых данных (ее значение ниже скорости передачи) одной линии шины необходимо учесть кодировку передаваемой информации. Как видно из таблицы данные передаются с избыточностью: 8 бит передаются 10 битами или 128 бит передаются 130 битами. Причина избыточности – исключить передачу большого количества идущих подряд нулей и единиц, затрудняющих распознавание со стороны приемника.

Год выпуска Версия PCI-Express Кодирование Скорость передачи Пропускная способность на x линиях, Гбит/сек x1 x2 x4 x8 x16 1.0 8b/10b 2,5 ГТ/с 2.0 8b/10b 5 ГТ/с 3.0 128b/130b 8 ГТ/с ~7.877 ~15.754 ~31.508 ~63.015 ~126.031 4.0 128b/130b 16 ГТ/с ~15.754 ~31.508 ~63.015 ~126.031 ~252.062 Чипсет

Логику взаимодействия всех комплектующих материнской платы персонального компьютера осуществляет чипсет – набор микросхем системной логики.

Чаще чипсет состоит из пары микросхем – так называемых Северного и Южного мостов. Северный мост обеспечивает связь между высокоскоростными компонентами вычислительной системы (процессор, оперативная память, видеоплата). Южный мост – связывает Северный мост со всеми прочими компонентами, работающими на меньших скоростях.

Как видно из рисунка, за несколько десятков лет для связи различных типов устройств было разработано множество видов шин. Некоторые из них меняли свое исходное предназначение, перемещаясь вниз по скоростной иерархии.

Для процессора разрабатывались высокоскоростные шины, например, FSB, DMI, HyperTransport и QPI.

Примером внутренних шин служат PCI и PCI-Express. Причем в последнее время PCI-Express все больше вытесняет шину PCI.

Примерами внешних интерфейсов для связи с накопителями могут быть IDE и SATA (современные накопители уже н оснащают интерфейсом IDE ).

Также разработаны внешние интерфейсы для связи с периферийными устройствами, например FireWire или USB.

Перечисленные интерфейсы относятся к наиболее популярным в настоящее время, но это лишь малая часть общего количества разработанных интерфейсов. Например, для медленных устройств, таких как BIOS, существуют низкоскоростные интерфейсы.

![]()

Высокоскоростные шины.

Рассмотрим кратко наиболее известные высокоскоростные шины, которые используются для связи процессора с чипсетом или для внутрипроцессорных взаимодействий.

FSB (Front Site Bus)

FSB – параллельная шина - разрабатывалась компанией Intel для связи процессора с северным мостом. Частота шины соответствовала частоте процессора, и возрастала с 50 МГц в начале 1990-х годов, до 400 МГц в конце 2000-х. Пропускная способность шины менялась с 400 Мбит/с до 12800 Мбит/с.

Шина FSB использовалась в процессорах типа Celeron, Pentium, Core 2 до 2008 года. На данный момент вытеснена шинами QPI и Hyper Transport.

Когда устройство ввода-вывода заканчивает свою работу, оно инициирует прерывание (при условии, что прерывания разрешены операционной системой). Для этого устройство выставляет сигнал на выделенную устройству специальную линию шины. Этот сигнал распознается микросхемой контроллера прерываний, расположенной на материнской плате. Контроллер прерываний принимает решение о дальнейших действиях

При отсутствии других необработанных запросов прерывания контроллер прерываний обрабатывает прерывание немедленно.

Если прерывание уже обрабатывается, и в это время приходит запрос от другого устройства по линии с более низким приоритетом, то новый запрос просто игнорируется. В этом случае устройство продолжает удерживать сигнал прерывания на шине до тех пор, пока оно не будет обслужено центральным процессором.

Для обработки прерывания контроллер выставляет на адресную шину номер устройства, требующего к себе внимания, и устанавливает сигнал прерывания на соответствующий контакт процессора.

Этот сигнал заставляет процессор приостановить текущую работу и начать выполнять обработку прерывания. Номер, выставленный на адресную шину используется в качестве индекса в таблице, называемой вектором прерываний, из которой извлекается новое значение счетчика команд. Новый счетчик команд указывает на начало соответствующей процедуры обработки прерывания. Обычно с этого места аппаратные и эмулированные прерывания используют один и тот же механизм и часто пользуются одним и тем же вектором. Расположение вектора может быть либо жестко прошито на аппаратном уровне, либо, наоборот, располагаться в произвольном месте памяти, на которое указывает специальный регистр процессора, загружаемый операционной системой.

Вскоре после начала своей работы процедура обработки прерываний подтверждает получение прерывания, записывая определенное значение в порт контроллера прерываний. Это подтверждение разрешает контроллеру издавать новые прерывания.

Благодаря тому, что центральный процессор откладывает выдачу подтверждения до момента, когда он уже готов к обработке нового прерывания, удается избежать ситуации состязаний при появлении почти одновременных прерываний от нескольких устройств.

Аппаратура всегда, прежде чем начать процедуру обработки прерывания, сохраняет определенную информацию. Сохраняемая информация и место ее хранения широко варьируются в зависимости от центрального процессора.

Как минимум сохраняется счетчик команд, что позволяет продолжить выполнение прерванного процесса.

Другая крайность представляет собой сохранение всех программно доступных регистров и большого количества внутренних регистров центрального процессора.

Место сохранения этой информации.

1. Один из вариантов состоит в том, чтобы сохранять эти данные в неких внутренних регистрах, доступных операционной системе.

Недостаток такого подхода — до тех пор, пока вся сохраненная информация не будет считана обработчиком прерываний, новые прерывания будет нельзя разрешать. Так как любое новое прерывание просто стерло бы всю сохраненную таким образом информацию, записав поверх нее новые данные. В результате прерывания оказываются запрещенными в течение довольно длительных интервалов времени, что приводит к возможному игнорированию некоторых сигналов прерывания от устройств и, соответственно, к возможной потере данных.

2. Поэтому большинство центральных процессоров сохраняют информацию в стеке.

Однако у этого подхода также имеются недостатки. В чьем стеке следует сохранять данные? Если использовать текущий стек, он может оказаться стеком процесса пользователя. При этом может даже выясниться, что пользователь использует указатель стека в своей программе весьма нестандартно, то есть стек может указывать на область памяти, в которой нельзя сохранять данные. Попытка записать несколько слов в стек в таком случае может привести к неисправимой ошибке. Также указатель стека может указывать на конец страницы памяти. После нескольких обращений к стеку указатель может достичь конца страницы памяти и вызвать соответствующую ошибку.

![]()

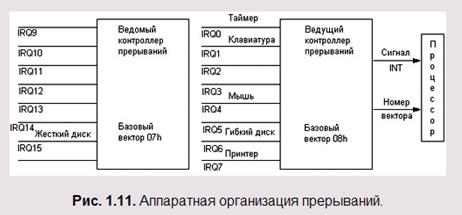

Сигналы аппаратных прерываний, возникающие в устройствах, входящих в состав компьютера или подключенных к нему, поступают в процессор не непосредственно, а через два контроллера прерываний, один из которых называется ведущим, а второй - ведомым (рис. 1.11)

![]()

Два контроллера используются для увеличения допустимого количества внешних устройств. Дело в том, что каждый контроллер прерываний может обслуживать сигналы лишь от 8 устройств. Для обслуживания большего количества устройств контроллеры можно объединять, образуя из них веерообразную структуру. В современных машинах устанавливают два контроллера, увеличивая тем самым возможное число входных устройств до 15 (7 у ведущего и 8 у ведомого контроллеров).

К входным выводам IRQ1. IRQ7 и IRQ8. IRQ15 (IRQ - это сокращение от Interrupt Request, запрос прерывания) подключаются выводы устройств, на которых возникают сигналы прерываний. Выход ведущего контроллера подключается к входу INT микропроцессора, а выход ведомого - к входу IRQ2 ведущего.

Основная функция контроллеров - передача сигналов запросов прерываний от внешних устройств на единственный вход прерываний микропроцессора. При этом, кроме сигнала INT, контроллеры передают в микропроцессор по линиям данных номер вектора, который образуется в контроллере путем сложения базового номера, записанного в одном из его регистров, с номером входной линии, по которой поступил запрос прерывания. Номера базовых векторов заносятся в контроллеры автоматически в процессе начальной загрузки компьютера.

Для ведущего контроллера базовый вектор всегда равен 8, для ведомого - 70h.

Таким образом, номера векторов, закрепленных за аппаратными прерываниями, лежат в диапазонах 8h. Fh и 70h. 77h.

Очевидно, что номера векторов аппаратных прерываний однозначно связаны с номерами линий, или уровнями IRQ, а через них - с конкретными устройствами компьютера. На рис. 1.11 указаны некоторые из стандартных устройств компьютера, работающих в режиме прерываний. Процессор, получив сигнал прерывания, выполняет последовательность стандартных действий, обычно называемых процедурой прерывания.

Подчеркнем, что здесь идет речь лишь о реакции самого процессора на сигналы прерываний, а не об алгоритмах обработки прерываний, предусматриваемых пользователем в программах обработки прерываний.

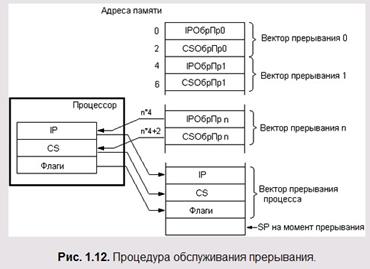

Объекты вычислительной системы, принимающие участие в процедуре прерывания, и их взаимодействие показаны на рис. 1.12.

![]()

Самое начало оперативной памяти от адреса 0000h до 03FFh отводится под векторы прерываний - четырехбайтовые области, в которых хранятся адреса обработчиков прерываний (ОбрПр на рис. 1.12).

В два старшие байта каждого вектора записывается сегментный адрес обработчика, в два младшие - смещение (относительный адрес) точки входа в обработчик.

Векторы, как и соответствующие им прерывания, имеют номера, причем вектор с номером 0 располагается, начиная с адреса 0, вектор 1 - с адреса 4, вектор 2 - с адреса 8 и т.д.

Вектор с номером n занимает, таким образом, байты памяти от n*4 до n*4+2.

Читайте также: